数据中心的演进:DDR5 DIMM整体提高服务器性能

简介

1981年IBM个人电脑(PC)和1984年苹果Macintosh的出现,对更大容量、更快速度的随机存取存储器(RAM)起到了重要的推动作用。这些系统使计算机进入了数百万人的办公室和家庭。一个快速的良性循环随之而来:越来越复杂的应用需要更多的计算能力,而计算能力需要更大更快的内存,从而实现更复杂的应用。

几十年后,平板电脑和智能手机等消费类设备将现有内存技术的界限推向了极限,基于云计算和超大规模数据中心的兴起也是如此。

超大规模的数据中心。这些大规模的数据中心包含由数十万台服务器组成的机架,配备先进的多核和多线程CPU,处理由智能手机、个人电脑、游戏机、物联网设备、支持高级驾驶辅助系统(ADAS)的车辆等产生和消费的泽字节(1021字节)的数据。在这一环境中,AI/ML训练和推理等工作负载推动着数据洪流的指数级上升。

DDR5标准旨在满足广泛使用情况下对高效内存性能日益增长的需求,如超大规模数据中心的高性能服务器。具体而言,DDR5支持更高容量的DRAM器件,使服务器和系统设计者能够在单片封装中使用密度高达64Gb的DRAM。与其前身DDR4相比,有许多显著的改进。利用这些优势需要解决更高速度和更低电压的信号完整性设计挑战。在本白皮书中,我们将仔细研究DDR的历史、2021年及以后的内存趋势,以及DDR5内存的优势和设计考虑。

第一部分:DDR DRAM的历史

DDR1-DDR3

双倍数据速率(DDR)存储器的历史可以追溯到20世纪80年代末,当时IBM设计的DRAM采用了双边时钟功能。利用双沿时钟技术,时钟信号的前缘和后缘都可以用来发送一个比特。因此,数据速率将是时钟速率的两倍。

然而,直到1997年,三星才展示了它的第一个DDR内存原型,随后在1998年6月首次推出了商用64兆(Mb)DDR SDRAM芯片。现代电子(现在的SK hynix)在同年晚些时候推出了其DDR SDRAM。

DDR(1)SDRAM通过在每个时钟周期内传输两次数据,有效地实现了比其前代SDRAM速度提高2倍(200至400 Mb/s)。此外,DDR1的特点是内存中有多个库,可以单独寻址。这使得DDR SDRAM能够提供多个交错的内存访问,从而提高了有效带宽。

DDR2 SDRAM--与第一代DDR的前身相比,它提供了更高的时钟频率和加倍的吞吐量--于2003年首次亮相。然而,新的DDR2内存缓冲器无意中造成了延迟问题,是DDR的两倍,并且需要将总线速度提高一倍来缓解延迟。到2004年底,具有明显低延迟的新模块开始广泛使用。最终,DDR2 DRAM的数据速率达到了400至1066 Mb/s。

2007年亮相的DDR3成功地保持了内部时钟速率,并通过加倍的预取深度支持更高的有效传输速率(800至2133 Mb/s)。除了更快的数据速率外,DDR3还降低了电源电压,减少了功耗,具有8个库和一个8位预取缓冲器,以及4个(活动)模式寄存器。此外,DDR3芯片上市时的初始容量为512Mb,最终实现了8千兆比特(Gb)的容量。

DDR4和DDR5

2014年首次推出的DDR4规定设备容量最高为16Gb。这使得双线内存模块(DIMMs)的容量高达64GB,而DDR3的每个DIMM最大容量为16GB。DDR4的初始每针数据速率被规定为1.6Gb/s,而最初的最大目标是3.2Gb/s。正如JEDEC固态技术协会所指出的,DDR4架构是一个8n预取,有两个或四个可选择的库组。这种设计允许DDR4内存设备支持单独的激活,以及在每个独特的库组中进行的读、写或刷新操作。这种架构提高了整体的内存效率和带宽,特别是在使用小的内存颗粒时。

DDR5标准于2020年7月由JEDEC正式发布。DDR5支持的带宽是其前身DDR4的两倍,预计将以4.8Gb/s的速度推出;比DDR4寿命终止时的最高速度3.2Gb/s高50%。事实上,该标准提供了两倍的性能和更高的能效,以满足云和企业数据中心应用的密集计算要求。据JEDEC称,DDR5旨在满足包括客户系统和高性能服务器在内的各种使用情况下对高效性能日益增长的需求。具体而言,DDR5标准的架构是为了在更高速度下实现内存性能的扩展而不降低通道效率。

第二部分:2021年及以后的内存趋势

在各种大趋势的推动下,全球数据流量正在以几乎指数级的速度增长。例如,5G网络正在使数十亿由人工智能驱动的物联网设备摆脱有线网络的束缚,而人工智能/ML对巨大数据集的贪婪欲望正以每年10倍的速度飞速增长。用于娱乐和商业应用的数据密集型视频流继续加速,随着游戏和电子竞技的普及,全球有近10亿玩家,对4K图形的需求不断增加。最后,不断发展的ADAS系统为复杂的自动驾驶车辆提供动力,增加了另一股数据洪流。

没有什么地方比数据中心更能感受到所有这些增长的影响。事实上,超大规模的数据中心已经成为全球数据网络的关键枢纽。使得数据中心成为 "超大规模 "的原因是它的架构允许可重复和快速部署计算能力,以满足客户的需求。

计算能力,以满足特定工作负载的需求。超大规模是更多商业应用和数据库从企业数据中心转移到云端的持续地震式转变的基础。截至2020年中期,全球共有541个超大规模数据中心,另有176个处于不同的发展阶段。这意味着自2015年以来,运营中的超大规模数据中心的数量翻了一番。

正如《EE Times》的Anton Shilov所指出的,DRAM的发展通常遵循与CPU发展相似的方向。可以肯定的是,微处理器正在不断向更高的核心数量发展,提高每个核心的性能,并提高电源效率。所有这些因素都影响并最终决定了系统对系统内存的要求。可以肯定的是,先进的内核要求增加内存带宽,而同时不断发展的工作负载要求更高的DRAM容量和带宽。

DDR5 DRAM有望通过同时向多个方向发展DRAM来满足下一代客户和服务器系统的要求。与其前身DDR4相比,DDR5的每引脚数据传输率提高了一倍,内存设备的容量增加了4倍,降低了工作电压和功耗,并引入了几种方法来提高DRAM在更小工艺节点上的可靠性。下面将探讨DDR5相对于DDR4的这些优势以及更多的优势。

第三部分:DDR5与DDR4 DIMMs的比较

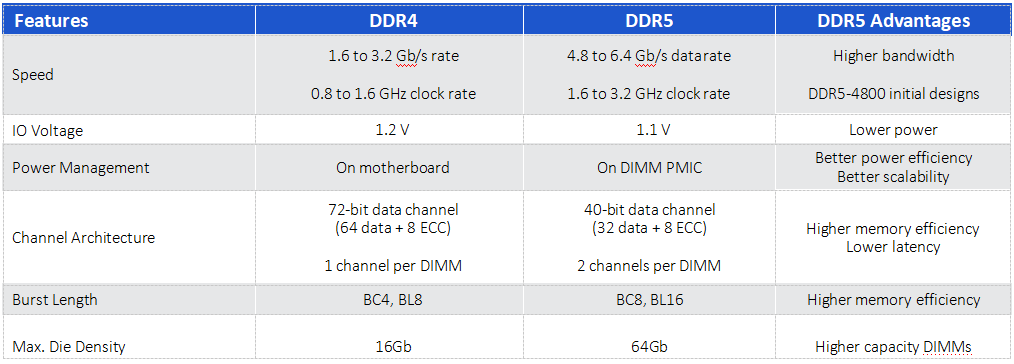

在本节中,我们将深入研究从DDR4到DDR5 DIMMs过渡过程中取得的最重要的六项规格进展,如下表1所强调。

Table 1. DDR5 advantages over DDR4 DIMMs

1.DDR5可扩展至6.4Gb/s

虽然DDR4 DIMM在1.6千兆赫兹(GHz)的时钟速率下最高速度为3.2Gb/s,但最初的DDR5将提供50%的带宽,达到4.8Gb/s。根据该标准,DDR5内存最终将使DDR4 DRAM的数据速率翻倍,达到6.4Gb/s。SK hynix甚至宣布了将DDR5提升至8.4Gb/s的计划。新的功能,如决策反馈均衡(DFE),被纳入DDR5中,以实现更高的I/O速度。

2.低电压意味着低功率

DDR5降低了工作电压(VDD),从而降低了功率消耗。有了DDR5,DRAM和缓冲器芯片的注册时钟驱动器(RCD)电压从1.2V降至1.5V。

然而,系统设计者必须认识到,更低的VDD意味着更窄的抗噪范围。

3.新的电源架构

随着DDR5 DIMMs的出现,电源管理从主板转移到DIMM本身。DDR5 DIMMs在DIMM上有一个12-V的电源管理IC(PMIC),使系统电源负载的颗粒度得到改善。PMIC分配1.1 VDD电源,通过更好地在DIMM上控制电源,帮助解决信号完整性和噪音问题。

4.DDR5与DDR4通道架构的比较

DDR5具有一个新的DIMM通道架构。DDR4 DIMM有一个72位总线,由64个数据位和8个ECC位组成。有了DDR5,每个DIMM将有两个通道。每个通道将是40位宽。32个数据位和8个ECC位。虽然数据宽度是相同的(总共64位),但有两个较小的独立通道可以提高内存访问效率。

在DDR5 DIMM架构中,DIMM的左侧和右侧分别由一个独立的40位宽通道提供服务,共享RCD。在DDR4中,RCD每侧提供两个输出时钟。在DDR5中,RCD每侧提供四个输出时钟。在具有x4 DRAM的最高密度DIMM中,这允许每组5个DRAM(单等级,半通道)接收自己的独立时钟。给每个等级和半通道一个独立的时钟,可以提高信号的完整性,有助于解决降低VDD(来自上述第2项变化)所带来的低噪声系数问题。

5.更长的突发长度

DDR4的突发斩波长度为4,突发长度为8。对于DDR5,突发斩断和突发长度将被延长到8和16,以增加突发有效载荷。突发长度为16(BL16),允许单个突发访问64字节的数据,这是典型的CPU高速缓存行大小。它可以只使用两个独立通道中的一个来完成这个任务。这在并发性方面有了很大的改善,而且有了两个通道,内存效率也更高了。

6.DDR5支持更高容量的DRAM

第六个也是最后一个需要强调的变化是DDR5对更高容量DRAM设备的支持。有了DDR5缓冲芯片DIMM,服务器或系统设计者可以在一个单片封装中使用密度高达64Gb的DRAMs。DDR4在单片封装(SDP)中的最大容量为16Gb DRAM。DDR5支持片上ECC、错误透明模式、封装后修复以及读写CRC模式等功能,以支持更高容量的DRAM。更高容量设备的影响显然转化为更高容量的DIMMs。因此,虽然DDR4 DIMMs的容量可以达到64GB(使用SDP),但基于SDP的DDR5 DIMMs将其容量翻了四倍,达到256GB。

第4部分:DDR5设计考虑因素

尽管DDR5显然比其前身DDR4提供了显著的改进和优化,但新的内存标准引入了与更高速度和更低电压有关的多种设计考虑因素,引起了新一轮的信号完整性挑战。更具体地说,设计者将需要确保主板和DIMM能够处理更高的信号速度。在进行系统级模拟时,应检查所有DRAM位置的信号完整性。

对于DDR4设计来说,主要的信号完整性挑战集中在双数据速率的DQ总线上,而对低速的指令地址(CA)总线的关注较少。对于DDR5设计,即使是CA总线也需要特别注意信号的完整性。对于DDR4,曾考虑使用差分反馈均衡(DFE)来改善DQ数据通道。然而,RCD在DDR5芯片上的CA总线接收器也需要DFE选项来确保良好的信号接收。

主板上的电源传输网络(PDN)是另一个考虑因素,包括直到带有PMIC的DIMM。鉴于更高的时钟和数据速率,设计者将希望确保PDN能够处理以更高速度运行的负载,并为DIMM提供最佳的信号完整性和清洁的电源。此外,从主板到DIMM的DIMM连接器必须能够处理新的时钟和数据速率。由于印刷电路板(PCB)周围的时钟速度和数据速率更高,必须更加重视系统设计的电磁干扰和兼容性(EMI和EMC)。

利用DIMMs的DDR5的优势

幸运的是,DDR5内存接口芯片大大提高了从主机内存控制器发送到DIMMs的命令和地址信号的完整性。每个通道的总线,两条通道的总线进入RCD,然后扇出到DIMM的两半。RCD减少了主机内存控制器 "看到 "的CA总线上的负载。简单地说,DDR5数据缓冲器芯片有效地减少了数据总线上的负载,使DIMM上更高容量的DRAM不会降低延时。

结论

基于云的计算和超大规模数据中心的兴起,将现有内存技术的界限推向了极限。这正是DDR5被设计用来满足高性能服务器需求的原因。

DDR5提供了更高容量的DRAM设备,使服务器或系统设计师能够利用高达64Gb的DRAM密度,在基于DDR5 SDP的DIMM中达到256GB的容量。有了DDR5,数据速率上升到6.4Gb/s,甚至有可能上升到8.4Gb/s,以提供对内存的高带宽访问。

虽然DDR5比其前身DDR4有显著的改进,但更高的速度和更低的电压带来了一系列新的信号完整性设计挑战,需要解决。幸运的是,Rambus公司的DDR5内存接口芯片大大改善了信号完整性,简化了DIMM设计,这将推动下一代服务器的性能。