基于Innovus的复杂时钟结构分析及实现

作者:曾晋伟

(深圳市中兴微电子技术有限公司,四川 成都 610041)

摘要:

在先进工艺节点下,随着设计规模越来越大,时钟频率越来越高以及时钟结构越来越复杂,愈发的发现最终整个设计收敛对于时钟质量的依赖越来越明显。针对类似多输入动态mux复杂时钟,IP模块多内部输出时钟等复杂的时钟结构,采用分析时钟框图及基于Innovus工具从网表中提取时钟结构的分析方式进行时钟结构上的详细梳理,提出针对时钟结构分析及clock spec的优化方法。同时在一个超大规模的16nm top design上基于优化后的clock spec进行CTS,并结合multi-tap的clock tree做法,从得到的结果可以发现在run time,clock latency等方面都有较大的提升,能够满足项目要求的时钟长度等要求,有效避免block接口的时序冲突。

关键词:Innovus;物理实现;时钟树;Multi-tap CTS

中图分类号:TN402 文献标识码:A

0 引言

随着集成电路工艺进入先进节点(Advanced Node),以及应用场景的不断增加,带来芯片设计规模越来越大以及时钟结构更加复杂,针对时钟结构的分析与时钟的实现也更加困难。就时钟树综合(Clock Tree Synthesis,CTS)而言,时钟结构复杂程度的增加,可能会带来公共路径(Common Path)的长度减少,片上误差(On Chip Variation,OCV)的影响增加,CTS迭代时间(turn-around time)增加,以及时钟上功耗增加等问题。因此,在物理实现中,CTS变得越来越重要。

在本文中,借助于Cadence公司的自动化布局布线工具Innovus,首先探讨了针对复杂时钟结构的时钟如何进行分析,其次基于分析结果提出时钟实现上可能出现的问题以及解决方案,再次,基于调整进行CTS实现,并与传统CTS方案的结果进行对比,最后对本文进行总结并对结论进行进一步分析。

1 复杂时钟结构概述

1.1 定义

本文中,复杂时钟结构主要指符合如下条件的时钟:

1)同一个sink点存在很多个时钟源头;

2)芯片规模很大,时钟实现可用区域有限,时钟长度(clock latency)要求很高;

3)时钟上逻辑关系复杂,比如时钟树上的逻辑单元和锁相环(PLL)之间对拥塞(congestion)及时序(timing)非常敏感,分频结构较为复杂,同一时钟下的不同sink点可能存在于不同的skew中,且不一定有时序交互(timing talk)。

1.2 复杂时钟结构CTS实现的挑战

一般情况下,针对复杂时钟结构时钟树,CTS实现上主要存在如下挑战:

1)目标clock latency要求较短,common path由于时钟结构本身的关系可能天然导致长度较短,OCV影响较大,各模块接口时序收敛难度较大;

2)时钟偏斜(skew)要求较高,特别是针对例如时钟频率超过1 GHz的高频时钟,skew很可能超过时钟周期的10%;

3)静态功耗以及动态功耗要求较高,信号电迁移(Signal EM)不能出现有违例(violation)的点。

1.3 传统CTS流程

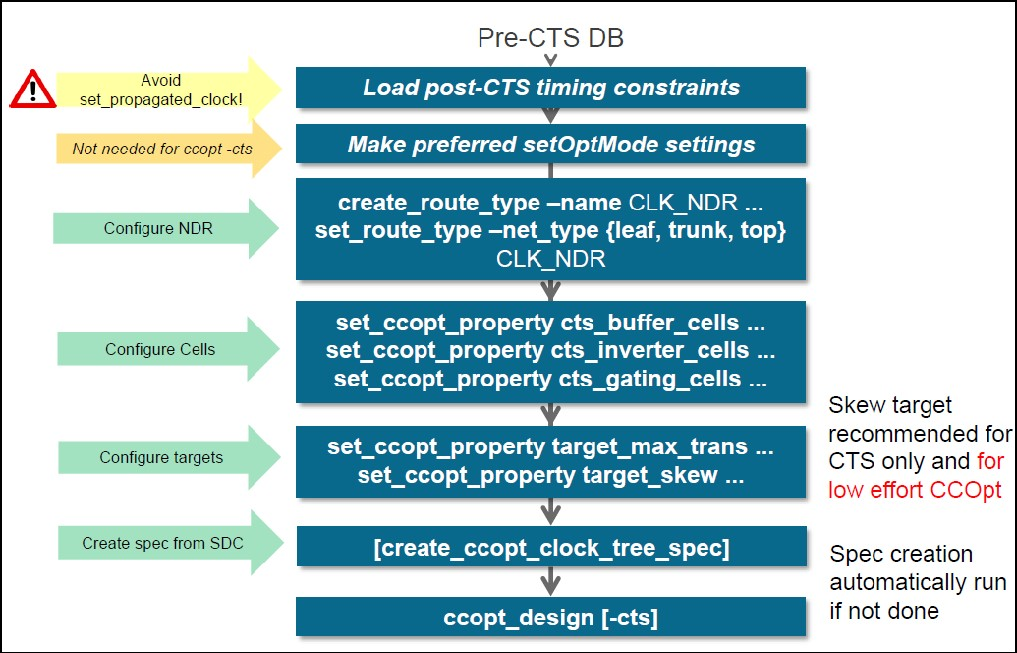

传统的CTS流程,一般来说都是首先读入CTS前的数据(database,DB),然后设置NDR(Non-Default Rule),CTS用到的cell,CTS target等信息,创建时钟定义文件(CTS spec),然后利用工具进行时钟树综合。具体的流程图如下:

图1 传统CTS流程图[1]

1.3.1 采用传统CTS流程存在的问题

传统CTS流程自动化程度很高,但是同样也存在一些问题,具体主要有以下几点:

1)在进行时钟树平衡(Balance)的时候,通常只会考虑一个单独的慢工艺角(slow corner),并且会在整个时钟树的所有位置利用单元插入(cell insertion),单元大小变化(cell sizing),以及走线长度的调整(wire length adjustment)等方式来达到预设的时钟树综合目标;

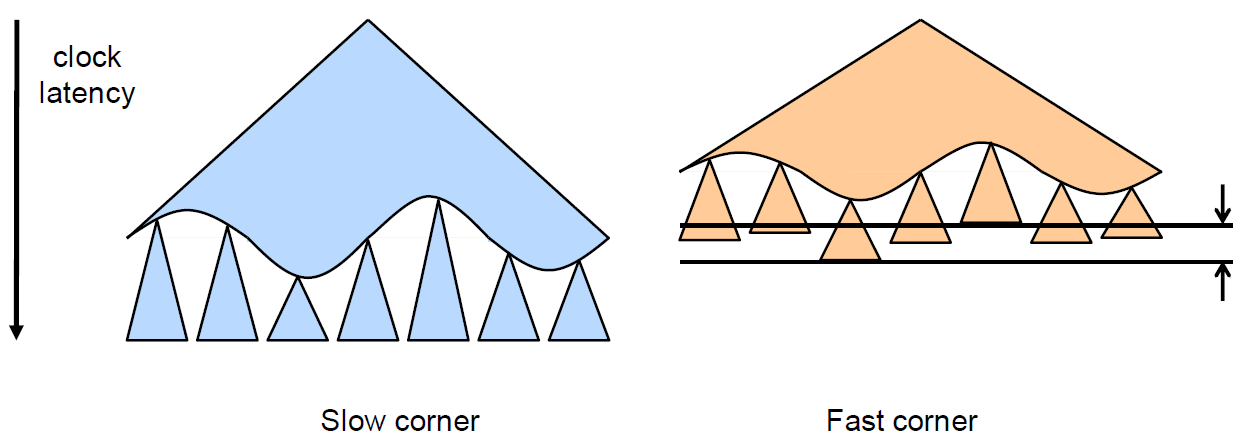

2)针对快工艺角(fast corner),电阻电容寄生参数(RC Parasitic Parameters)的变化会导致在slow corner下balance的时钟树在fast corner下变得不balance,skew可能会增加;

3)高频路径可能会有建立时间(setup time)和保持时间(hold time)之间的冲突,对时序收敛造成风险。

图2 同一时钟不同corner下的skew差异[2]

1.3.2 采用传统CTS流程实现复杂时钟结构存在的问题

复杂时钟结构如果采用传统的CTS流程,主要会面临如下问题:

1)由于时钟结构复杂,自动生成CTS spec文件的时间可能会非常长,通常可能超过10小时,对于迭代来说这个时间是非常不利的;

2)自动生成的CTS spec文件中,针对不同skew group下的冲突sink,一般不会针对性做特殊处理,最终可能导致时钟长度很长;

3)如果设计中存在是时钟需要走在窄沟道(narrow channel)或者不友好的路径(un-friendly path)的情况,可能导致某些CTS cell放置位置不合理导致CTS结果不理想的情况。

2 复杂时钟结构实现方法学

本部分基于一个实际的例子,来描述如何利用Innovus工具来实现复杂时钟结构的CTS。

2.1 设计介绍

本部分采用了一个基于TSMC 16nm工艺的一个芯片顶层来进行说明。整个芯片的大小大约为22mm*16mm,共有超过60个模块,最高金属层为M11,其中M9及以下层次可以用于信号走线,最高频率超过1GHz,各模块接口时序为同步,仅顶层有超过26万个寄存器,其中打拍寄存器超过一半,Signoff方式为AOCV(Advanced-OCV)。

Floorplan大致如下图,其中灰色部分为top only逻辑:

图3 Floorplan图

2.2 基于Innovus的时钟结构分析

本部分中,我们基于Cadence公司的Innovus工具,对时钟结构进行分析,主要的分析方式主要有Schematic Viewer和Ccopt clock tree debugger两种。

2.2.1 时钟结构分析

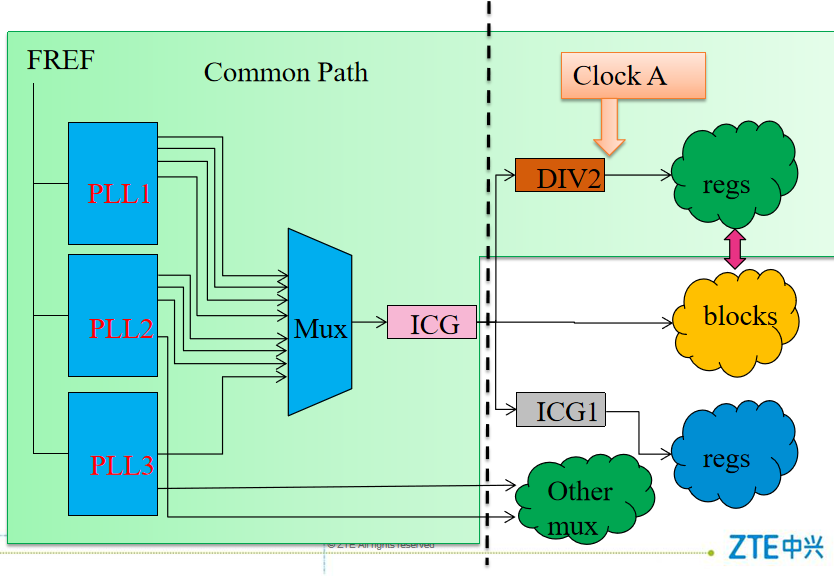

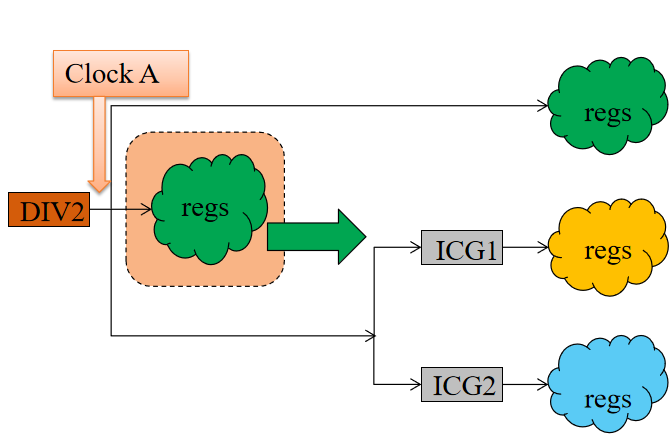

图4 时钟结构框图

如图4,我们以图中Clock A为例,可以看到,分频器后定义了generated clock,且top和block之间接口时序检查的时钟即为Clock A,在ICG1后的寄存器和分频器(DIV2)后的寄存器之间无时序检查。

具体的时钟结构中,mux为8输入动态mux,总共输入8个频点,所有到模块的时钟为原始频率,且在block内部进行分频,然后用于接口,分频时钟在top only也用于部分异步桥逻辑。

物理位置上,PLL1和PLL2距离很近,但和PLL3距离较远,且PLL2和PLL3还会输出其余频点给别的逻辑进行使用。

利用Innovus工具,我们也可以得到8输入动态mux的具体结构由100多个与非,或非以及时钟门控等单元组成,且根据要求,所有的这些时钟逻辑单元需要在实现的时候设置成dont_touch。

2.2.1 复杂时钟结构实现

针对复杂时钟结构,通常我们会采用分析时钟结构后,提取出关键信息,利用增加region,预摆放时钟cell,以及调整cts spec,采用multi-source方式进行时钟实现等方式来实现。

2.2.1.1 Region调整

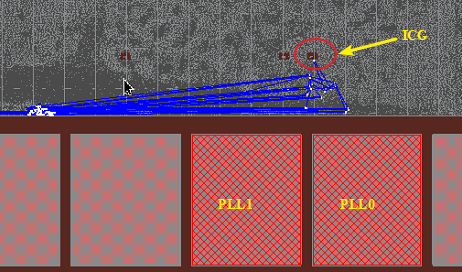

如图5上图为增加region前,可以看到动态mux的时钟逻辑cell被工具放置在距离PLL较远的位置,通过设置region,可以得到如图5下图的效果,将时钟逻辑cell放置到PLL边上,保证时钟在绕线的时候不detour。

图5 增加region前后时钟cell位置

2.2.1.2 spec调整

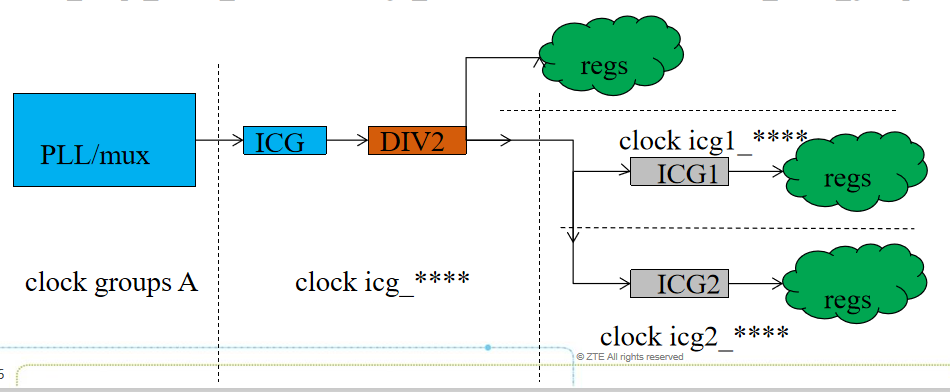

图6 时钟结构细化

基于时钟结构的具体分析,我们对Clock A后的寄存器分为两类,一类为没有二级ICG单元的控制,一类为有二级ICG单元控制的,且这类还可以再根据ICG的不同细化为两类(ICG1,ICG2)。

以上三类寄存器之间没有相互的timing talk。

图7 时钟拆分

在spec中,我们将整条时钟利用ICG作为分隔点的不同拆分成三个:

create_ccopt_clock_tree -name icg_**** -source ****ICG/Q -no_skew_group

create_ccopt_clock_tree -name icg1_**** -source ****ICG/Q -no_skew_group

create_ccopt_clock_tree -name icg2_**** -source ****ICG/Q -no_skew_group

从而,整条clock tree最终会被拆分成4部分,如图7所示。

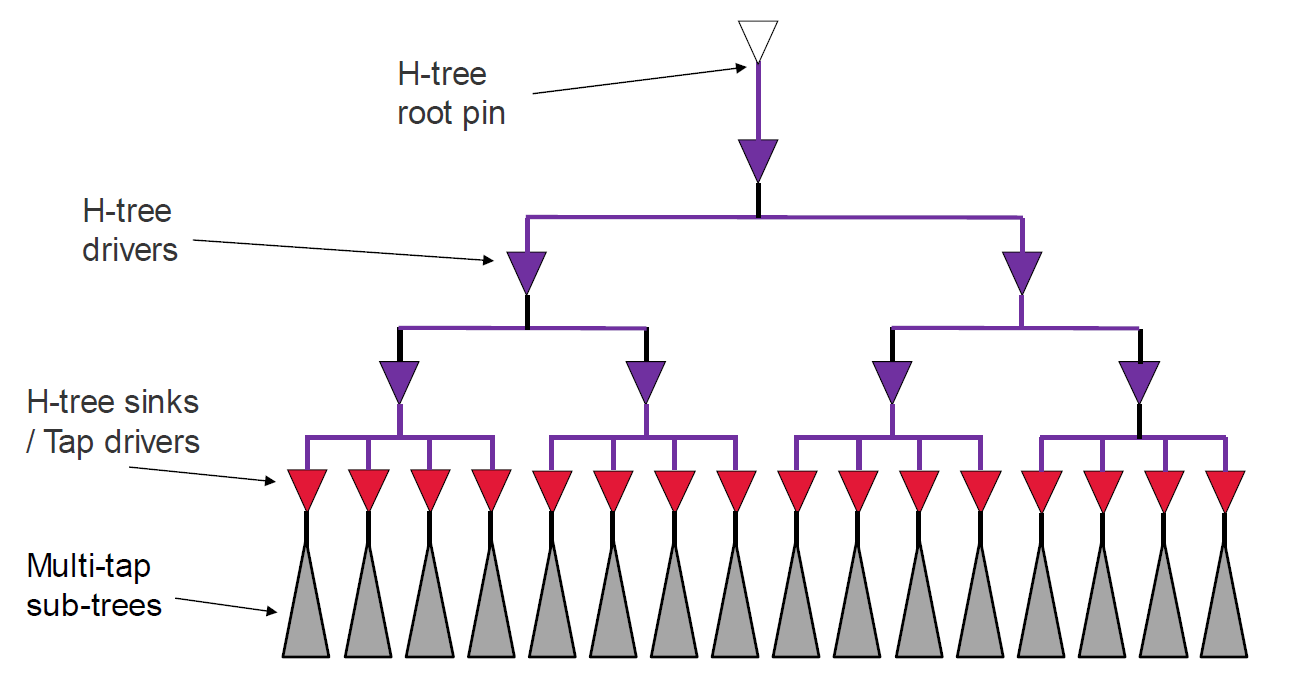

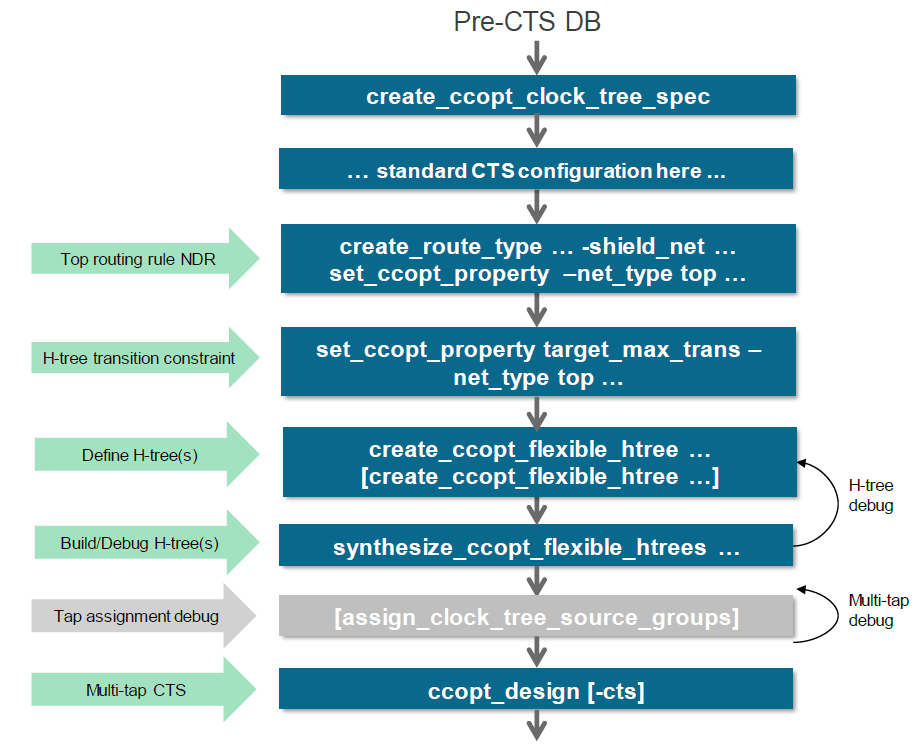

2.2.1.3 multi-source clock tree实现

在本部分,我们介绍如何利用Innovus工具进行multi-source clock tree实现。

Multi-source clock tree为一种基于传统CTS方法的基础上,提出的更加高级的clock实现方法,可以有效降低时钟长度,从而达到OCV影响的减少,具体的示意图及流程图如图8。

图8 Multi-source CTS 示意图及流程图[1]

针对图8步骤的H-tree部分,为了更好的降低clock latency,我们预先用24倍的反相器(Inverter)以及高层金属(M10,M11)提前进行预先绕线。但是为了降低天线规则,压降(IR-drop),EM等方面的影响,采用大驱动inverter需要做如下处理:

1)所有的24倍Inverter周围预留15um左右的位置用于填DCAP cell,降低因为驱动较大可能造成的IR drop;

2)所有的24倍Inverter针对性的加密电源网络,避免出现电源上的EM问题;

3)增对可能出现的天线效应,提前放置二极管cell等进行规避;

4)Signal EM方面,采用NDR规则走线,增加打孔,以达到规避。

在用multi-source CTS流程中,在执行完assign_clock_tree_source_groups后,我们可以从log中看到每一个tap点对应的cell分布,通常情况下都是很均匀的分布,且sink点距离tap点的位置符合预期,如果出现异常点,则需要具体分析该tap点后的sink异常的原因。

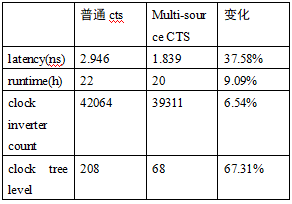

2.3 结果对比

结论

针对复杂结构的时钟树,利用工具来进行时钟结构的识别及分析,可以在CTS甚至pre-CTS等阶段有效提高效率。

针对时钟结构中的同一时钟下的没有时序检查的寄存器,设置skew group来调整balance策略,可以有利于时钟树做短。

采用大驱动的时钟反相器并通过multi-source的方式长clock tree,同样也是一种有效减少时钟长度的方式,并且针对受OCV影响较大的设计,这种方式也可以有效减少迭代时间,加速时序收敛。

参考文献

[1].Cadence Innovus User Guide[EB/OL].[2020-5-21]https://www.cadence.com

[2].Flexible H-tree and Multi-Tap Clock Flow in Innovus[EB/OL].[2020-5-21] https://www.cadence.com

作者简介

曾晋伟(1991-),男,工程师,主要研究方向:数字集成电路物理实现。