SerDes如何成为半导体系统的关键IP?

By Eric Esteve (PhD.) Analyst, Owner IPnest

我们已经看到,接口类IP在过去20年里以惊人的速度增长,而且我们预计这一类别至少在未来十年内会产生持续的高额IP收入来源。但是,如果我们深入研究各种成功的协议,如PCI Express、以太网或USB,我们可以在物理(PHY)部分发现一个共同点,即串行器/解串器(SerDes)功能。

1998年,电信应用中使用的高级互连基于622 MHz LVDS I/O芯片制造商正在制造集成256个LVDS I/O的超大芯片,运行频率为622MHz,以支持网络架构。今天,先进的PAM4 SerDes的运行速度为112 Gbps, 通过单个连接即可支持100G以太网。二十年来,SerDes的技术效率跃升了180倍! 如果我们快速比较一下CPU技术, 1998年,英特尔发布了奔腾II Dixon处理器,其频率是300 MHz。 在2018年,英特尔酷睿i3以4 GHz运行, CPU频率增长了15倍,在长达20年的时间里,SerDes的速度猛增了180倍。

SerDes现在被用于比电信更多的应用中,用于连接芯片和系统。在2000年代末,智能手机集成了USB3、SATA 和HDMI接口,而电信和PC/服务器集成了PCIe和以太网。这些趋势导致接口IP市场成为一个相当大的IP类别, 当时增长超过2亿美元。与CPU类别相比,CPU类别是它的四到五倍。但是,自2010年以来,接口类的增长率每年至少达到15%。与所有其他半导体IP类别(如CPU、GPU、DSP、Library 等)相比,它是增长最快的类别。其中的原因与每年连接的设备数量增长直接相关,彼此交换更多的数据(更多的电影、图片等)。连接是通信链的起点,连接到internet调制解调器或基站、以太网交换机和数据中心网络。

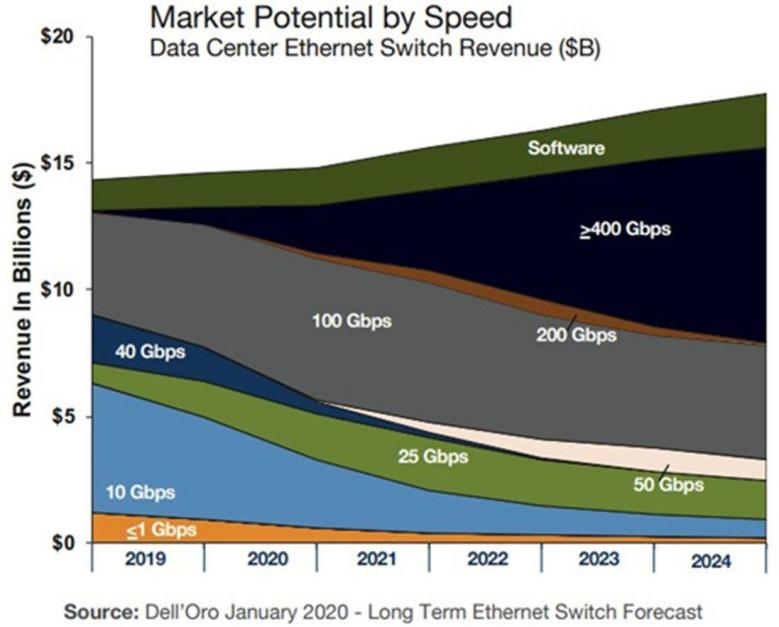

图1:以太网交换机长期预测(来源:Dell'Oro)

在2010年到2020年的十年里,世界范围内的所有群体几乎完全联系在一起。随着连接速率和数据中心数量在过去十年中迅速增加,以太网成为这种连接的主干。如果我们使用SerDes速率作为指标,它在2010年为10 Gbps,2013年为28 Gbps,2016年为56 Gbps(分别支持10G、25G和50G以太网),2019年为112 Gbps。

然后,在2017年,新兴数据密集型计算应用(如机器学习和神经网络)对高速连接需求的急剧上升,增加了对高带宽连接的日益增长的需求。同时,由于CMOS技术向先进的FinFET发展,模拟混合信号体系结构(从一开始就是SerDes设计的标准)变得极其难以管理,并且对工艺、电压和温度变化更加敏感。

在现代纳米FinFET技术中,考虑到晶体管的微小尺寸,构建晶体管需要堆叠单个电子。因此,建造精确的模拟电路来承受压力环境的变化是极其困难的。

但像7nm这样的先进技术的优点是,你可以以平方毫米(每平方毫米1亿个晶体管的密度)集成数量惊人的晶体管,因此,现在有可能利用数字信号处理(DSP)开发新的基于数字的架构来完成绝大部分的物理层工作。 与以前的历史模拟混合信号方法所使用的不归零(NRZ或PAM2)相比,基于DSP的体系结构可以使用更高阶的脉冲幅度调制(PAM)调制方案。

PAM 4使信道的数据吞吐量在不增加信道本身的带宽前提下翻倍。例如,具有28ghz带宽的信道可以使用NRZ信令支持56gbps的最大数据吞吐量。随着PAM-4dsp技术的使用,同样的28ghz带宽信道现在可以支持112gbps的数据速率!当您考虑到模拟SerDes体系结构由于物理原因(可能更少……)被限制在56 Gbps的最大速率时, DSP SerDes是一种通过使用更复杂的调制方案(例如PAM-6或PAM-8)将速率扩展到200 Gbps及以上的方法。

在FinFET技术中,使用基于DSP的SerDes不仅是构建耐用的接口所必需的,而且也是在56gbps以上将数据速率加倍的唯一方法,例如,PAM-4为112gbps,PAM-8为200gbps。而这种对更多带宽的需求与新兴的数据密集型应用程序如AI(连接CPU和加速器)、ADAS和以数据为中心的互联人类社区趋势相关,预计在未来十年内将稳步增长。

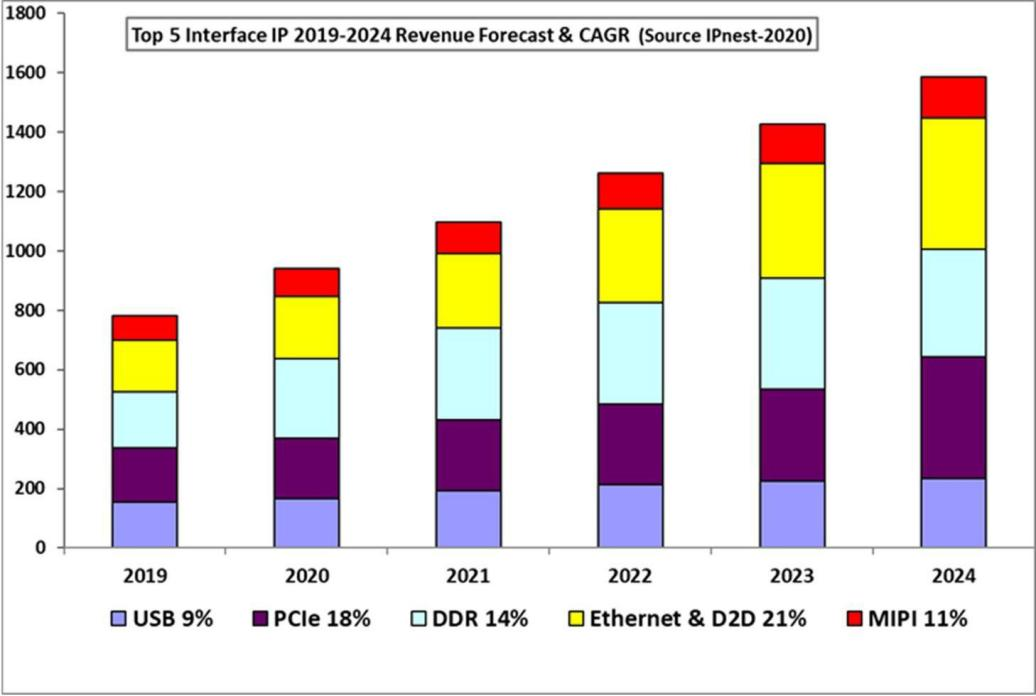

图2:IP预测和复合年增长率前5名(来源:IPnest 2020)

在“接口IP调查”中,IPnest按协议对2009年以来IP供应商收入的市场份额进行了排名。在2020年版的报告中, 我们已经表明,从2020年到2024年,接口IP类别的复合年增长率将达到15%,达到15.7亿美元,如图2所示。这是一个广泛的IP市场,包括PCIe、以太网和SerDes以及USB、MIPI、HDMI、SATA和内存控制器IP。2019 年,Synopsys在估计8.7亿美元的IP市场中占据53%的市场份额,其主导地位毋庸置疑。其次是Cadence,占12%。

两家EDA公司都定义了一站式的商业模式,面向主流市场。这一战略对这些大公司来说是成功的,因为它针对的是各种细分市场(智能手机、消费者、汽车或数据中心)的广泛部分,而不是这些细分市场中要求最高的高端部分。

然而,另一个策略对于IP市场是成功的,那就是将重点放在一个细分市场(如高端市场),并为要求非常高的客户提供最佳体验。如果你能建立一个优秀的工程团队,能够用最先进的技术开发出高质量的产品,专注于高端市场,那么由此产生的商业模式将是值得的。

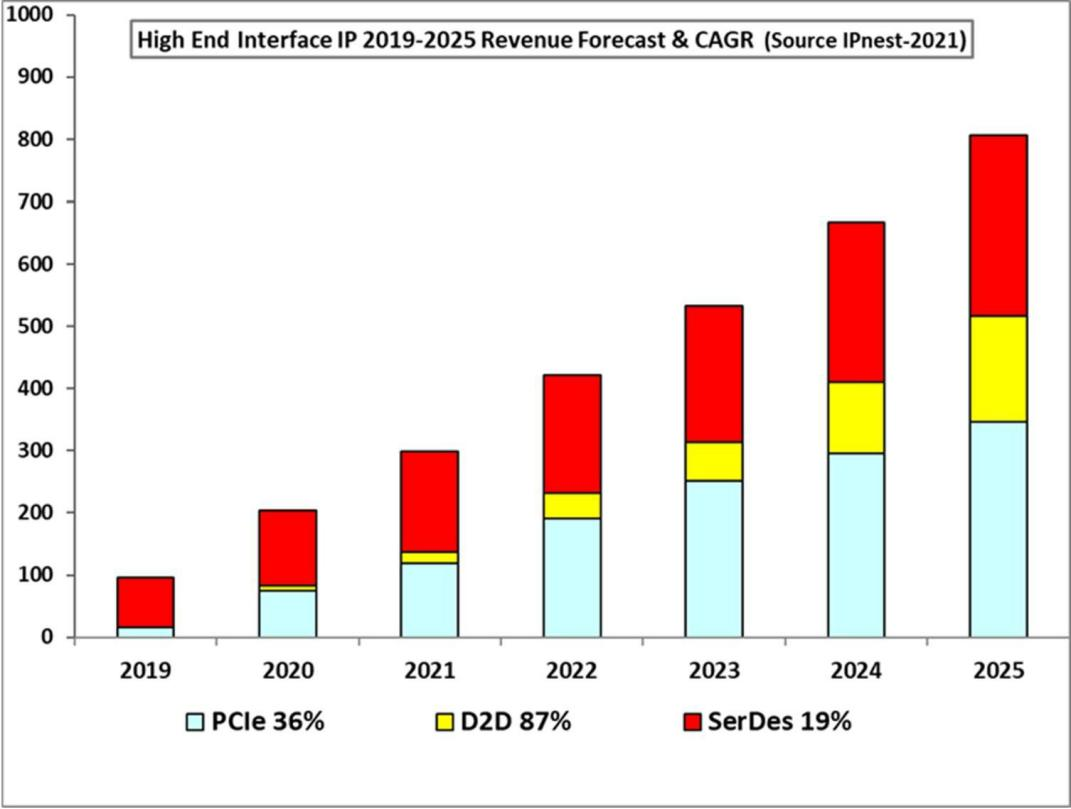

我们已经看到SerDes IP是接口IP市场的关键。此外,如果我们专注于PCIe和以太网协议,图3说明了2020-2025年的IP收入预测,仅限于高端PCIe(第5代和第6代)和高端以太网(基于56G、112G和224G SerDes的PHY),其中包括D2D协议,原因将在稍后介绍。

图3:高端接口IP预测和复合年增长率(来源:IPnest 2021)

这一高端接口IP预测显示,在2020-2025年其复合年增长率为28%(相比之下,接口IP市场的总复合年增长率为15%),到2025年,TAM将达到8.06亿美元。

一家年轻的公司在高端接口IP领域表现出了强大的领导能力,这得益于他们专注于高端SerDes(2017年起为112G,很快将为200G),由两家领先的铸造厂TSMC和三星提供的最先进的技术节点(2017年为7nm,2019年为5nm)。

Alphawave成立于2017年,据传其在2020年的订单为7500万美元,这得益于其定位是针对最先进的速率和高端PCIe 以及以太网细分市场的应用。在这部分市场中, 它们在2019年和2020年的市场份额分别为28%和36%。如果Alphawave能够在高端SerDes市场保持领先地位,那么预计到2024-2025年,IP收入将达到3-4亿美元并非不现实!

自2019年以来,出现了一个新的细分市场,即D2D接口,预计2020-2024年复合年增长率将达到46%。根据定义,D2D协议在一个普通的硅封装中用于两个芯片或芯片之间。简单地说,我们考虑了两种D2D情况:i)主SoC的不集成,以避免SoC面积严重影响产量或变得大于最大掩模尺寸,或ii)SoC与“服务”芯片(可以是i/O芯片、FPGA、加速器……)互连。

在这一点上(2021年2月),正在使用多种协议,业界试图为其中的许多协议建立正式的标准。 当前领先的D2D标准包括:i)英特尔最初定义的高级接口总线(AIB,AIB2),提供了免版税使用; ii)高带宽内存(HBM)高级SerDes IP成为现代半导体的关键©2021 IPnest 6,其中DRAM裸片彼此堆叠在硅中介层的顶部,并使用TSV连接;iii)领域特定体系结构(ODSA)子组是一个行业组织,它还定义了另外两个接口,电线束(BoW)和OpenHBI。

所有这些D2D标准都基于类似DDR的协议,这是一组平行的单端数据线,与当前在2GHz到4GHz范围内工作的转发时钟相配合。通过在非常短的距离上使用数百条并行线,这些接口与VHS SerDes NRZ竞争,通常定义在40 Gbps左右,与SerDes相比,提供了更低的延迟和更低的功耗的强大优势。

目前业界普遍认为,疯狂地关注摩尔定律的做法对先进技术节点(如7nm及以下)不再有效。芯片集成仍在进行,每平方毫米都会增加更多晶体管。然而,每一个新节点的每一晶体管成本都在不断增加。芯片组技术是一项关键举措,它在使用旧的主流节点来服务芯片组的同时,推动主SoC的集成度的提高。这种混合策略降低了直接将服务IP集成到主SoC中所带来的成本和设计风险。IPnest认为,这一趋势将对接口IP业务产生两大影响, 一是D2D IP收入(2021-2025)会呈现强劲增长,另一个是创建异质芯片市场,以扩大高端SerDes IP市场。

我们对2020-2025年D2D接口IP类别的增长进行了预测,从2020年的不足1000万美元增长到2025年的1.71亿美元(复合年增长率87%)。这一预测是基于这样一个假设:2023年服务芯片市场将会爆发式增长,届时大多数高级SoC将在3nm内设计。这将使得像SerDes这样的高端IP的集成风险太大,导致将这一功能外化到以7或5nm 等更成熟节点设计的芯片中。

如果接口IP厂商将成为这场革命的主要参与者,那么解决最先进节点(TSMC和Samsung等)和制造主要SoC的硅铸造厂将发挥关键作用。我们不认为他们会设计芯片,但他们可以决定支持IP供应商,并推动他们设计出用于3nm SoC的芯片组,就像他们今天支持先进的IP供应商将他们的高端SerDes作为7nm和5nm硬IP推向市场时所做的那样。英特尔最近向第三方代工厂的转型有望同时利用第三方IP,以及半导体重量级企业采用的异质芯片。在这种情况下,毫无疑问,像微软、亚马逊和谷歌这样的超标量公司也将采用芯片体系结构……如果他们在芯片采用方面甚至没有先于英特尔的话。