PCIe组合平台—从片上PCIe交换到长距PCIe

1. 简介

日益增长的人工智能和数据分析工作负载, 正在推动现代企业对IT基础架构中新计算和新存储的需求。加速器(如:GPU,FPGA,定制ASIC)和新兴内存技术(如:3D XPoint,存储类内存,非易失性内存)的使用不断增长,以及更好地分配和利用这些资源的需求,推动了向可组合/分解基础结构(CDI)的过渡。

随着这种格局的变化,出现了许多互连协议(NVMe-oF,CCIX,Gen-Z,CXL),有望解决可组合性模型带来的挑战。尽管这些互连技术日趋成熟并逐渐成为主流,但系统供应商仍然可以利用成熟的PCI Express协议来实现可扩展、可组合的各种选择。

在本文中,我们描述了最常见的选项,并提出了一种新趋势,其中涉及将片上PCIe交换和电缆上的PCIe传输相结合,以构建智能,可扩展的高性能可重构系统。

2. 带PCIe交换芯片的结构

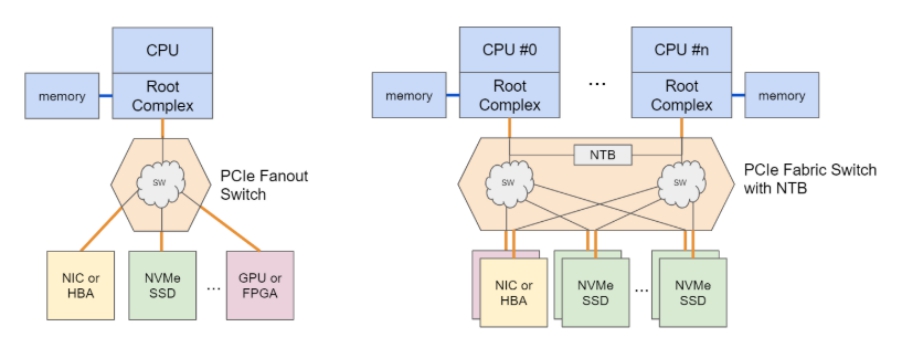

PCIe交换芯片由PLX(Avago)和Microsemi(Microchip)等公司提供已有十多年的历史。这些PCIe交换芯片已发展为允许多种使用模式,从使用PCIe透传交换的简单PCIe扇出扩展到使用非透传桥接(NTB)的更复杂的PCIe架构拓扑,如图1所示。

图1 – PCIe交换拓扑结构示例

尽管OEM,ODM和许多系统厂商广泛使用透传PCIe交换进行扇出扩展,但非透传的光纤交换机本质上更加复杂,依靠定制的NTB软件进行操作,因此更加难以集成和部署。即使像Liquid和Dolphin Interconnect Solutions这样的公司将基于PCIe架构的解决方案推向市场时,使用分立交换芯片来构建PCIe互连架构也存在一些局限性:

•特定应用芯片(ASSP)具有固定的体系结构和功能集,这意味着它们可能未得到充分利用或不完全适合该应用

•这些芯片通常会在至少18至24个月的时间内跟踪PCIe规范的新修订,因此可能无法提供最新功能和最佳性能。

•增加了总体物料清单(BoM),增加了功率预算并在系统中引入了新的故障点

•当围绕相同的ASSP构建这些产品时,系统供应商构建差异化产品变得越来越困难

对于那些正在设计自己的芯片的技术公司来说,考虑将PCIe交换功能嵌入其SoC中是有道理的,那就是以差异化面向未来的设计, 实现其应用程序所需的特定功能集。

3. 具有PCIe交换IP的片上系统

SoC架构师现在可以选择将PCIe交换IP集成到他们的设计中。这种方法的主要好处是:

•PCIe交换IP可以与SoC的CPU复合体和内存子系统集成在一起,从而减少了解决方案的时延和硅片面积.

•PCIe交换IP可以根据应用程序的确切需求进行配置。配置选项通常包括:端口数量,每个端口的通道数量,每个端口的PCIe链接速度,点对点通信,端口仲裁,低功耗支持等。

•可以添加在线数据包处理功能(需要PCIe交换IP支持),例如数据包筛选,数据包检查,加密和其他功能,以减轻系统CPU的负担

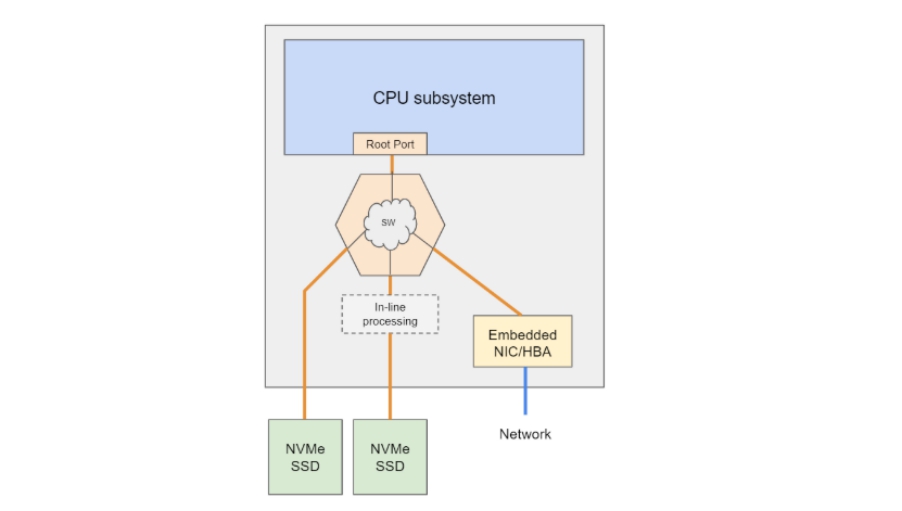

•嵌入式端点功能(例如NIC功能,自定义加速器)可以实现,以优化成本(BoM,硅面积),且因无需使用PCIe PHY而减少延迟和功耗,如图2所示。

•架构师可以进一步定义交换逻辑,以定制或添加功能,例如自定义端口仲裁方案,自定义路由表/规则等。

图2 - 具有透传交换IP和嵌入式端点的SoC

端点的功能可以通过使用虚拟化进一步扩展,从而允许在多个虚拟机之间共享资源。

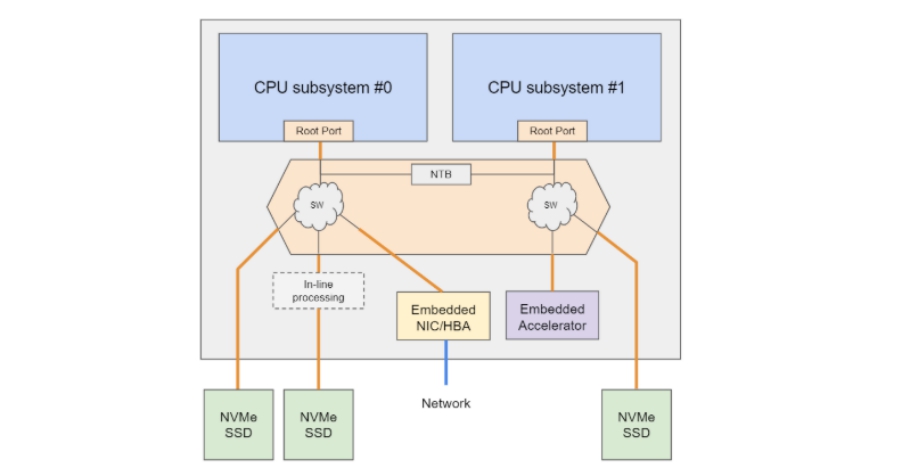

SoC中实例化的多个交换机IP以及允许跨不同PCIe域进行通信的NTB机制可支持多个主机域,如图3所示。

图3 - 具有两个通过NTB连接的PCIe域的SoC

4. 通过长距PCIe扩展服务器范围

16GT / s PCIe 4.0信号在标准FR4 PCB上只能传播3到5英寸,而没有经过任何连接器。 改用MEGTRON 6 PCB并添加重定时器IC有助于改善传输距离,但是成本却大大增加。

随着光通信产品成本的优化,现在大规模部署16GT / s传输PCIe 4.0信号长达数百英尺所需的基础架构已成为可能。

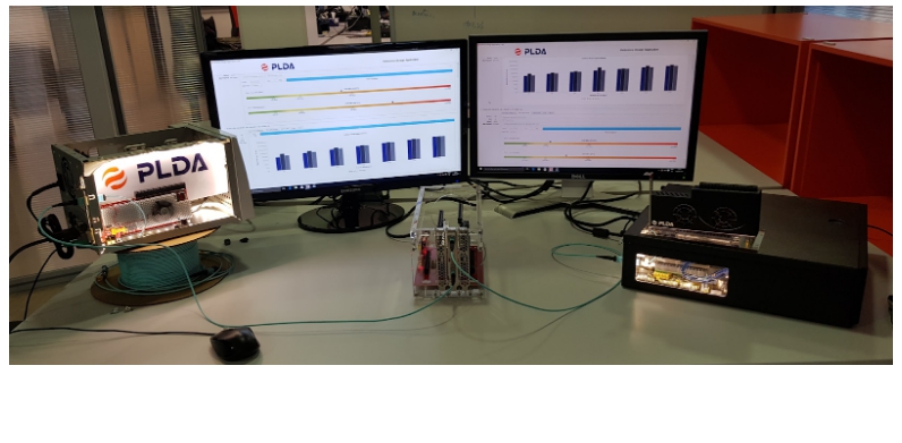

我们的最新实验(如图4所示)显示了一条PCIe 4.0 x4链路,该链路在330英尺的光缆上连接了两个对等端,虽有轻微的延迟损失,但对数据吞吐量没有影响。

图4 – 光纤PCIe交换网演示实例

5. 组合到一起

我们看到希望将智能交换功能集成到其基于PCIe的SoC中的芯片设计人员的数量正在增加。 对于图2和图3概述的体系结构类型,PLDA XpressSWITCH透传交换机IP正在成为行业的标杆解决方案,客户早在2016年就已开始部署。XpressSWITCH的主要功能包括:

•支持32GT / s的PCIe 5.0规范

•完全可配置的解决方案:下行端口数量,每个端口的链路宽度和链路速度,低功耗模式,热插拔等

•支持PIPE连接的嵌入式端点

•通过嵌入式端点支持NTB

•先进的机制,例如广播,组播,DPC

•使用LCRC,ECRC,奇偶校验和ECC进行存储器的数据保护

•超低延迟切换逻辑

•无缝实现ASIC和FPGA平台上的实现

•广泛支持各种PCIe PHY

图5 提供了XpressSWITCH IP的体系结构概述。

图5 - XpressSWITCH IP架构

XpressSWITCH IP是PLDA用于PCIe的INSPECTOR的核心,这是一种具有诊断功能的主机平台,自2016年以来已在PCI-SIG Compliance Workshops中用于PCIe 4.0 FYI互操作性测试。

如通过Samtec FireFly™Micro Flyover System™所展示的,通过将XpressSWITCH IP与PCIe在光学介质上的传输相结合,系统厂商可以进一步扩展光纤网络的覆盖范围,以构建完全可分立的基于PCIe的平台。

6. 结论

可分立又可组合的基础设施, 正在定义下一波数据中心架构。虽然出现了新的存储器语义结构和通信协议以实现这种模式转变,但这些技术在芯片上实现到数据中心可部署可能还需多年。

同时,SoC设计人员正在寻找利用成熟的PCIe协议构建智能高性能结构的方法。随着光通信成本的不断优化,SoC还能够跨距离在芯片外跨距离传输PCIe数据流,而对性能的影响最小,从而实现了基于PCIe的分解架构。

通过使用诸如PLDA XpressSWITCH之类的现成PCIe交换机IP,IC设计人员发现了一种灵活的方式来构建可组合的PCIe系统,从而使他们能够在功能和特性方面定义和控制解决方案的各个方面,并最终创建差异化产品。

要了解有关XpressSWITCH交换机IP的更多信息,请访问我们的产品页面:www.plda.com/cn