Innovus机器学习在高性能CPU设计中的应用

边少鲜1,Micheal Feng 1,David Yue1,栾晓琨1,蔡准2,蒋剑锋1

(1. 天津飞腾信息技术有限公司,湖南长沙 41000; 2. 上海楷登电子科技有限公司,上海201204)

摘要:

高性能芯片设计在7nm及更高级的工艺节点上,设计规模更大、频率更高、设计数据和可变性更复杂,物理设计难度增大。机器学习在多领域均获得成功应用,复杂的芯片设计是应用机器学习的一个很好的领域。Cadence 将机器学习算法内置到innovus工具中,通过对芯片设计数据进行学习建模,建立机器学习模型,从而提升芯片性能表现。建立了一个应用机器学习优化延时的物理流程来提升芯片设计性能。详细讨论分析了分别对单元延时、线延时、单元和线延时进行优化对设计的影响,进而找到一个较好的延时优化方案。最后利用另一款设计难度更大,性能要求更高的模块从时序、功耗、线长等方面较为全面的分析验证设计方案的合理性。

关键词:机器学习; innovus; 芯片设计; 物理设计

0 引言

摩尔定律揭示了集成电路的集成度和技术节点的飞速发展,这使得芯片设计的复杂度和数据量快速上升,尤其是芯片的物理设计更是设计海量的数据和信息,且运行时间和设计周期漫长,迭代一次的时间和资源代价很大,这对设计师的经验与能力要求很高。机器学习如今在各个领域都有广泛的应用,其能学习数据规律建立模型从而快速推断结果[1]。如果能在物理设计中应用机器学习挖掘设计规律,且基于推断的求解来进行物理设计,可加速芯片设计。国内外很多学者在此方面有了成功的研究,包括David Z. Pan等详细介绍的在物理设计中应用机器学习[2]。B.Li使用机器学习由全局布线线预测详细布线结果[3]。TSMC在物理设计中应用机器学习的两款芯片分别可使频率提升40MHz和减少20,000时钟门控单元等[4]。

本文基于Cadence Innovus工具建立应用机器学习进行延时优化的物理设计流程,研究7nm工艺下不同层金属的特性,设置三个实验组单元延时优化、线延时优化、单元和线延时同时优化与传统物理设计流程进行对比分析。同时将应用机器学习进行延时优化的物理设计流程应用到更大规模,设计复杂度更高的ARM架构的一款CPU设计中,均得到了很好地性能优化。最终确定了两款模块芯片均采用Innovus机器学习进行延时优化的物理设计流程。

1、机器学习介绍

机器学习计算机通过模拟人类学习思维过程以获取知识和技能来重构自身知识体系并改善自身性能的过程。机器学习可分为三部分:任务、模型和特征。常见的任务包括分类、归类、聚类、异常检测、排序等。常见的模型包括线性模型、支持向量机、智能神经网络等。特征包括统计特征、业务特征以及自动提取的特征[5]。

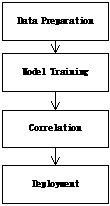

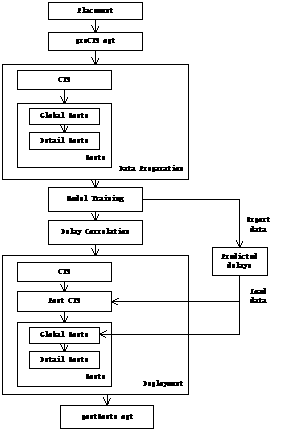

一般的机器学习流程如图1 所示,(1)数据准备,对收集到的数据进行分析处理产生模型训练的数据集和用于评估模型表现的参考数据。(2)模型训练,即确定合适的算法对数据集进行处理分析预测。(3)评估,训练完成后,通过真实数据与预测数据进行对比,评估模型的好坏。(4)模型部署,即将训练模型加载到设计中。

图1 机器学习流程

2、物理设计介绍

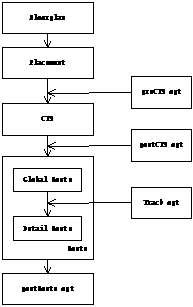

芯片的物理设计过程即将电路中所有的宏模块、门、晶体管等,用固定的形状和大小在制造层上表示,并进行空间位置分配(布局),然后用适当的金属线来完成逻辑连接的互连(布线),物理设计直接影响电路的性能、面积、功耗等。物理设计的起点是插入扫描链的门级网表,过程被分为一下几个关键步骤:布图规划、布局、时钟树综合、布线。在实际物理设计时,会在关键步骤间插入优化,如图2所示为Cadence Innovus的传统物理设计流程,其中布局之后、在时钟树综合之后以及布线之后均加入优化步骤。

2.1 物理设计布线

随着现代设计规模达到数百万计的网络,布线的计算复杂度成为关键,对于给定的设计,布局的总线长影响最大时钟频率,最大时钟频率主要依赖于线延时和单元延时,在早期工艺下,单元延时是电路延时的主要部分,在先进工艺下,尤其是7nm及更先进工艺下,互连线会产生相当大的信号延时,所以布线必须考虑线延时。布线的最终目标是在满足工艺规则、设计规则以及逻辑规则的约束下,将单元和I/O用金属连接起来的同时,使得总线长度最小,网络线延时最小。

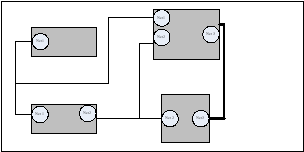

芯片物理设计的完整布线过程分为三个步骤:总体布线、详细布线和时序驱动布线。其中前两步如图3所示。总体布线如图3(a),是粗粒度通过网络拓扑结构,暂时分配资源到布线区域用于连接;详细布线如图3(b),是细粒度分配指定布线金属层到布线轨道;时序驱动布线是网络拓扑优化和资源分配到关键网络。

图2 Cadence Innovus传统物理设计流程

总体布线的目标是确定给定布局是否可布线,并在可布线区域确定所有网络的一个粗略布线。

详细布线过程包括若干中间任务和决定,例如网络排序和引脚排序,即哪些布线优先级高,以及一个网络中,引脚该按照怎样的顺序来连接。网络和引脚的排序会很大程度上影响最后的解质量,针对这个问题,很多EDA工具都有相应解决方案,比如Innovus的三步绕线方案。

(a)总体布线

(b) 详细布线

图3 网络Net1~Net3的图形表示

时序驱动布线的目的就是小范围内最小化驱动到负载的最大互连延时以及总线长。

2.2 传统物理设计流程的局限性

由2.1的介绍可知,详细布线力求完善总体布线,一般不会改变总体布线确定的线网规划,而时序驱动布线优势小范围操作,因此,如果总体布线的解不好,那么详细布线解的质量以及最终的布线结果都会受影响。布线的结果直接影响最终物理设计的质量。

2.3 Innovus 机器学习方案介绍

Innovus是业内主流的物理设计布局布线工具,可以提供合理有效的物理设计方案,在运行效率、时序分析、设计优化方面都体现出强大的功能[6]。Cadence在Innovus中内置机器学习算法来取代传统的算法,通过对大量芯片设计数据进行学习建立了一个可自动辅助芯片设计的机器学习模型,完成集成参数的提取,快速布线和运算等方面的工作。

3、7nm工艺下金属特性分析

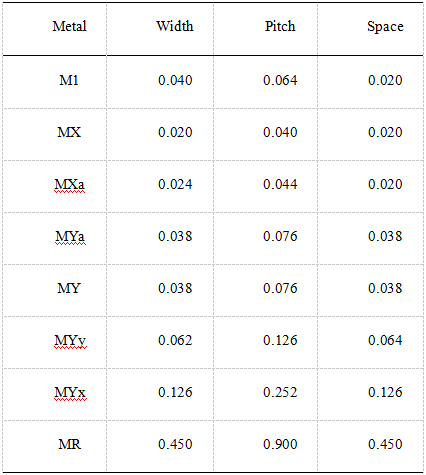

表1 7nm工艺下不同厚度金属物理尺寸规则 (um)

在利用Cadence Innovus工具应用机器学习进行延时优化的物理设计之前,先对7nm工艺下的金属特性进行分析,表1所示为工程所用7nm工艺下不同特性金属的物理尺寸规则。Width代表最小金属宽度,Pitch代表最小布线间距,Space代表最小金属间距。由于M1不用于布线,MX只用于连接单元引脚,所以后面分析不包括M1和MX。

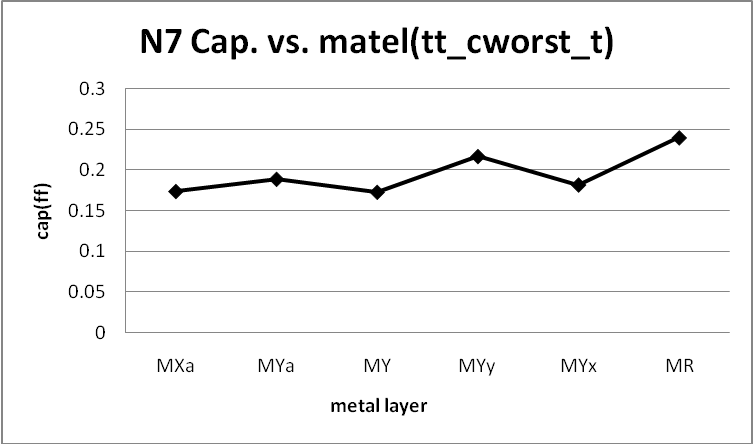

(a)单位距离下不同特性金属的C特性

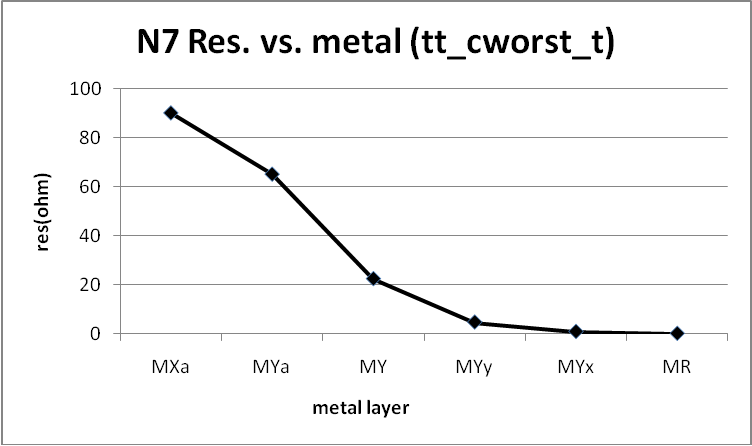

(b) 单位距离下不同特性金属的R特性

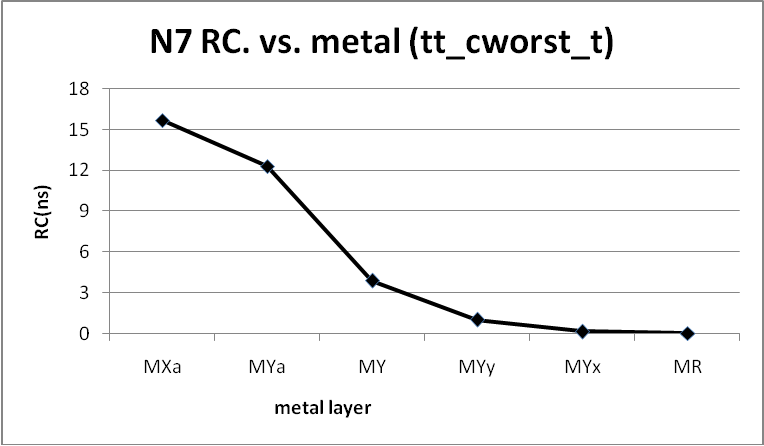

(c) 单位距离下不同特性金属的R*C特性

图4 单位距离下不同特性金属的RC特性

如图4所示为单位距离下不同特性金属的电阻(R resister)电容(C capacitance)特性。由图可知,在tt_cworst_t这个工艺角下,不同特性金属的电容C偏差较小,MR金属的电容C明显大于其他金属;不同特性金属的电阻R偏差较大,从低层金属到高层金属,电阻R几乎呈线性递减。图4(c)将电阻和电容做乘积,可见RC的变化趋势几乎与R的变化趋势相同。

CMOS电路中传输网络的信号延时为分段电阻和分段电容之积的和,可用Elmore延迟模型[7]来等效:

![]()

(1)式中和代表分段电阻,和代表分段电容。

由上可将金属线延时做如下(2)式等效

(2)式中R、C分别代表金属线的电阻电容。

由式(2)可知信号线延时正比于RC之积,由图4(c)可知,若要减小信号线延时可尽量多的使用高层金属布线。

4、应用机器学习进行延时优化

4.1 实验设置

图5所示为利用Cadence Innovus工具内置的机器学习算法进行延时优化的物理设计流程。先将做完布局后优化的数据库作为机器学习延时优化物理设计的起点。具体步骤:(1)数据准备:①不进行优化的时钟树综合;②总体布线;③详细布线;(2)模型训练:对数据准备阶段的数据库进行模型训练,导出模型训练结果;(3)延时数据对比;(4)模型部署:重新以做完布局后优化的数据库为起点,进行时钟树综合,在时钟树综合之后的优化以及总体布线过程中导入模型训练后的结果,最后完成布线后的优化。

图5 Innovus机器学习优化延时的物理设计的流程

4.2模型评估

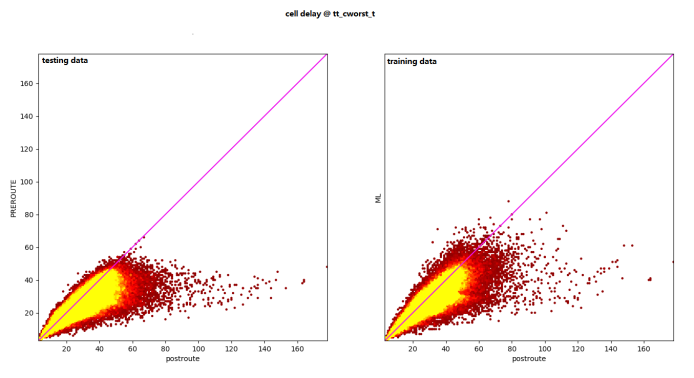

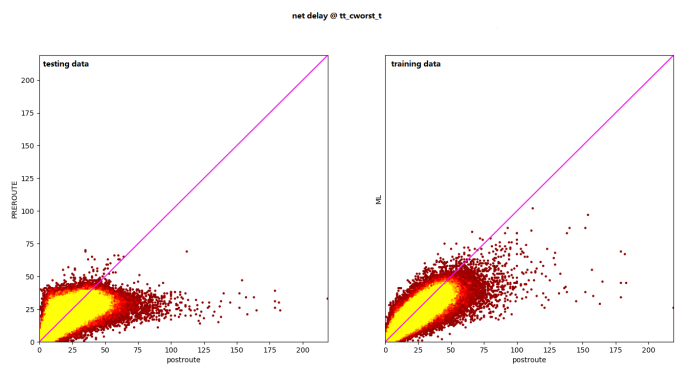

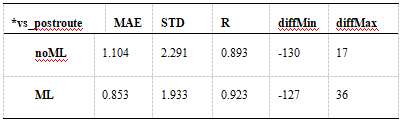

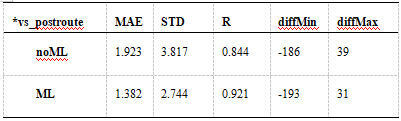

图6图7为详细布线前后单元和线延时的对照,其中左图纵坐标为未使用机器学习延时优化的测试组数据,右图纵坐标使用机器学习延时优化的训练组数据,横坐标均为详细布线后的结果,图形对角线代表详细布线前后延时精确匹配。对延时信息进行数理统计分析如表2、表3所示,表格中的MAE (Mean Absolute Deviation)代表平均绝对误差,STD(Standard Deviation,常用ơ表示)代表标准差,R代表相关系数,diffMin代表最小偏差,diffMax代表最大偏差。

(a)详细布线前后对照 (b)详细布线结果与机器学习预测对照

图6 详细布线前后单元延时对照

(a)详细布线前后对照 (b)详细布线结果与机器学习预测对照

图7 详细布线前后线延时对照

表2详细布线前后单元延时统计 (ps)

表3详细布线前后线延时统计 (ps)

由图6、7及表2、3可知,应用机器学习模型进行延时优化后,详细布线前后单元和线延时均呈现整体上相关性更强的趋势,而单元延时的标准差由2.291减小到1.923,即有99.7%的线延时偏差在3ơ(±5.799ps)以内,线延时的标准差由3.817减小到2.744,即有99.7%的线延时偏差在3ơ(±8.232ps),这比未应用机器学习进行优化的测试组延时偏差优化了28%。但单元延时最差偏差和最小偏差控制在(-1.270E+02,3.600E+01),明显大于未进行机器学习延时优化的测试组。

5、优化效果

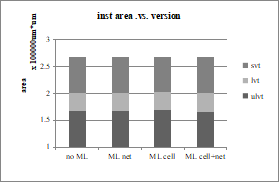

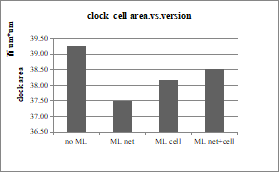

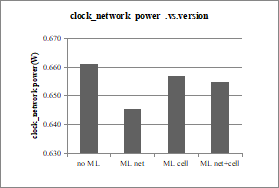

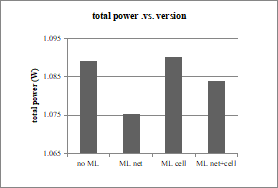

将4.2节分析的机器学习模型部署到某模块物理设计中,分别进行了只优化单元延时(ML_cell)、只优化线延时(ML_net)、同时优化单元延时和线延时(ML_net+cell)的优化实验,同时以不应用机器学习优化延时的传统物理设计流程为参照组(no_ML)。

下面从线、单元、功耗、时序四个角度分别就设置的4个对照实验进行物理设计结果的对比分析。

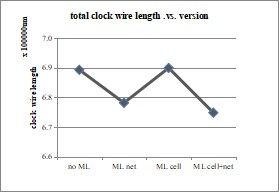

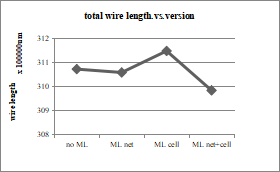

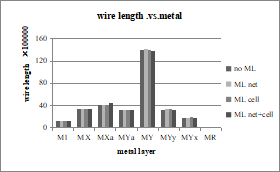

5.1 进行延时优化后的线网对比

由第2、3节分析可知,要减少线延时的关键在于减少线长和增加高层线的使用比例,而且详细布线过程中网络和引脚的排序会很大程度上影响最后的布线质量,而时钟树布线往往优先级最高。图8所示为4个实验组的总线长、时钟线长及金属层的分布。由图可知:(1)实验组ML_net+cell的线长最短,且时钟线最短,但是这组实验对金属层的选择较差,使用较多的低层金属;(2)实验组ML_net使用较多的高层线,且总线长较短,时钟线也较优;(3)实验组ML_cell则线长过长,且时钟线的长度最长。因此,就线而言,实验组ML_net和ML_net+cell表现较好。

(a)4个实验组的总线长情况

(b)4个实验组的金属层分布

(c)4个实验组的时钟线长情况

图8 4个实验组的线信息

5.2 进行延时优化后的单元对比

图9所示为4个实验组的实例化单元面积、不同阈值电压单元分布、时钟树单元面积。由图可知:(1)4个实验组的总实例化单元数量相差不明显;(2)不同阈值电压单元分布情况类似;(3)实验组ML_net+cell时钟单元总面积最小,实验组ML_net时钟单元面积略大于ML_net+cell,但仍明显小于其他两组。因此,就单元而言,实验组ML_net和ML_net+cell表现较好。

5.3 进行延时优化后的功耗对比

图10所示为4个实验组的总功耗及时钟网络的功耗情况。由图可知:(1)进行机器学习延时优化的三个实验组的时钟网络功耗均有不同程度减少;(2)实验组ML_net的总功耗和时钟网络功耗明显低于其他三组,实验组ML_net+cell次之。因此,就功耗而言,实验组ML_net表现最好。

(a)4个实验组的总实例化单元情况

(b)4个实验组时钟树单元面积情况

图9 4个实验组的单元信息

5.4 进行延时优化后的时序对比

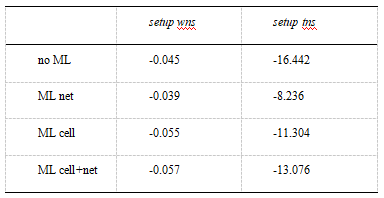

表4所示为4个实验组的时序情况。表格中wns(worst negative slack)代表时序违反最差路径,tns(total negative slack)代表所有时序违反路径的违反值之和。两表格中的setup和hold结果均为postroute阶段innovus报出的结果。从表4中setup wns和tns结果来看,(1)使用机器学习进行延时优化对setup tns均有不同程度的改善,且实验组ML_net在优化setup wns和tns方面均表现最好,比对照组优化50%;(2)使用机器学习对单元延时进行优化,会恶化setup wns;(3)使用机器学习单独针对单元延时或线延时进行优化,比既对单元延时又对线延时进行优化的时序结果好。因此,就时序优化结果来看,实验组ML_net表现最好。

(a)4个实验组总功耗情况

(b)4个实验组时钟网络上的功耗情况

图9 4个实验组的功耗信息

表4 4个实验组的时序情况 (ns)

综合上述分析结果,可知,(1)使用机器学习进行延时优化可对改善原有设计;(2)针对实验用Innovus版本,只对线延时进行优化效果最好。

6、方案一致性

表5 4个实验组的时序情况 (ns)

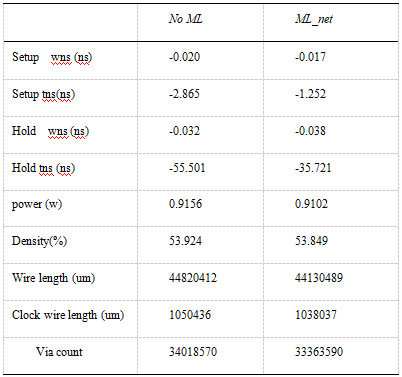

为确保第3节中得到的ML_net优化效果在其他模块中亦能体现,本节选取了一款340万门的ARM架构CPU模块芯片采用Innovus机器学习线延时优化物理设计流程,从时序、面积和功耗方面进行比较,结果对比如表5所示。

从表5中可以看出,该模块设计在应用Innovus机器学习进行线延时优化后,时序、功耗、线长等方面均得到不同程度的优化,其中timing尤其是TNS得到了明显提高,同时线长减小1.18%,功耗还降低了0.5%,这说明该流程在利用机器学习进行延时优化提升性能的时候,并没有以牺牲资源为代价,相反,由于延时更准确,还能更好地节省设计资源,这就充分证实了该方案流程的一致性。

7、结束

本文建立利用Cadence Innovus工具内置的机器学习算法进行延时优化的物理设计流程。实现了单独对线延时、单独对单元延时、同时对线延时和单元延时进行优化,最后确定只对线延时优化可得到更好的设计性能。同时将该流程应用到更大规模,设计复杂度更高的CPU设计中,同样得到了很好地性能优化。最终确定了两款模块芯片均采用Innovus机器学习进行延时优化的物理设计流程,实现setup和hold均比较容易收敛的同时减小功耗的结果。

参考文献

[1].B. Yu, D. Z. Pan, T. Matsunawa, and X. Zeng,Machine learning and pattern matching in physical

design. Proc. of the IEEE/ACM Asian and SouthPacific Design Automation Conference (ASPDAC),pp. 19-22, 2015

[2].B. Li and P. D. Franzon, “Machine learning inphysical design,” Proc. of the IEEE Conference onElectrical Performance of Electronic Packaging andSystems (EPEPS), pp. 147-150, 2016.

[3].http://isscc.org/2017/isscc-call-for-papers/abstract-submission/

[4].Bishop C M.Pattern Recognition and Machine Learning (Information Science and Statistics) [M].Springer,2006:1-4.

[5].LidaBai and Lan Chen.Machine-Learning-Based Early-Stage Timing Prediction in SoC Physical Design[J].IEEE,2018

[6].边少鲜,David He,等.基于Innovus提升芯片性能的物理实现方法[J].电子技术应用,2019,45(8):48-52.

[7].林铭波.超大规模集成电路系统导论[M].北京:中国工信出版集团,2015:213-214.

作者简介

边少鲜(1991-),女,本科,工程师,主要研究方向:数字后端物理实现。

栾晓琨(1981-),男,硕士,架构师,主要研究方向:数字后端物理实现。

蒋剑锋(1988-),男,硕士,工程师,主要研究方向:数字后端物理实现。