片上电感的优化设计

摘要:

本文从电感的性能指标入手,介绍了电感的性能指标(感值和品质因素)。接着阐述电感的损耗机理,最后提出了一些电感优化设计的方法。

前言

在 RFIC 应用电路中,电感往往占据了大部分面积,其相关参数在很大程度上会限制电路性能和表现,是影响低成本、低功耗、低噪声 RFIC 电路实现的关键元件。而电感是一种磁能储能元件,其配合电能储能元件(如电容)等能实现诸多功能,尤其是它的低通高阻特性使其广泛应用于降低电源电压、滤波等电路中。而片上螺旋电感相对于分立绕线电感,更低成本、更易集成、更小功耗、更少噪声,但却因其结构导致的诸多寄生效应而影响性能。为更好地理解、研究,本章将就 RF 片上螺旋电感的物理版图结构、常见性能指标、一般损耗机制、普遍建模方法作系统而简洁的介绍。

本文首先介绍了片上电感的性能指标,并分析了各指标对射频前端模块的影响。其次重点介绍片上电感的寄生效应和损耗机制,为电感的设计指明了优化方向。最后通过几个实例介绍了电感优化常用的一些方法。

片上电感分析

电感的性能指标

平面螺旋电感一般是利用标准CMOS工艺中的两层金属层来实现电感元件,一层作为螺旋电感的线圈主体,一层通过通孔与主体金属层连通,用作内圈金属跨接引出端口的引线。为远离有损衬底同时减小导体损耗,一般仅使用顶层及次顶层金属。

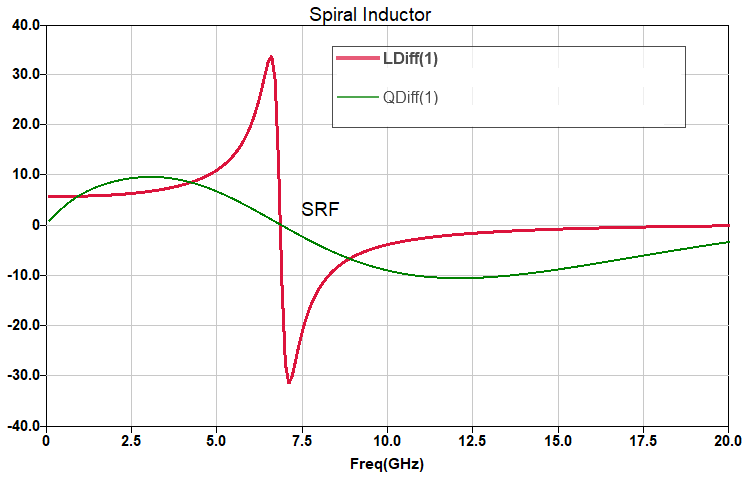

电感的性能指标:电感值?和品质因数?。随频率变化的情况如下图1所示。螺旋电感同时具有电感和电容特性,当寄生电容在一定频率下与电感发生共振时,我们称这个频率点为自谐振频率(SRF)。根据电感的频率特性,当电感感值基本不随频率变化而保持稳定,此时作为电路有意义的工作频段(图中为2.5G左右)。

图1:电感指标的频率响应

对于 RFIC 电路来说,片上螺旋电感的品质因数?定义为系统中存储的磁能与每个周期能量损失的比率。它决定了相关阻抗匹配网络的损耗,影响滤波器性能,电路带宽、有效功率、噪声等也都与之相关,因此品质因数是电感建模的常用验证指标。

电感的损耗机制

寄生和损耗是制约品质因数的主要因素,比如:端口电容,导体的趋肤效应、邻近效应,衬底涡流,由线圈-衬底寄生电容和衬底材料导致的传导和位移电流损耗等。它们可以分为三大类:金属损耗、衬底引发的损耗及其他寄生损耗(如端口间耦合寄生),以下主要介绍前两类。

金属损耗

基于 RF CMOS 制造工艺的片上螺旋电感,通常是由一层或多层金属构成,而现实中的金属总是具有有限的电导率,因此电流流经电感线圈时不可避免地会有能量损失,属于螺旋电感固有损耗,是限制低频器件性能的主要因素。

A.趋肤效应

一般情况下,导体的直流电阻(ρ为电阻率,?为导体长度,S为导体横截面积)。随着频率从直流逐渐升高,有效电阻出现了增大的趋势,主要原因是:当频率从 0 开始上升时,导体内电流由直流变为交变电流,时刻变化的电流产生时变电场,根据麦克斯韦电磁场理论,时刻变化的电场会产生时刻变化的磁场,磁场穿透导体并在导体内产生方向相反的感应电场,电、磁场交替感应、变化,使得原先均匀分布于导体内部的电流,在电磁场的作用下,趋向于向导体表面积聚,结果越靠近导体表面电流密度越大,且频率越高该现象越明显。趋肤效应导致导体的有效横截面积减小,因此伴随频率的升高,螺旋电感的有效电阻会在直流数值的基础上增大。高频下常用“趋肤深度?”来定义电流集中通过的导体表面薄层的厚度

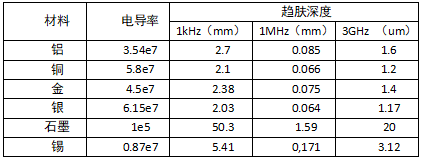

我们列出一般材料的趋肤深度如下:

B.邻近效应

在多导体系统中,某一导体附近的磁场被认为是自磁场和相邻磁场的共同作用之和。当两条处于高频条件下的导体相互靠近时,相邻磁场的作用会更强烈,导致导体内部电流的分布发生变化而偏向一边,此即导体的邻近效应,若相邻导体内流过的电流方向相同,则导体内电流会趋向各自外侧,反之若为反向电流,则会趋向内侧。对于螺旋电感而言,存在多组间距较近的金属条,因而邻近效应的作用十分明显,不容忽视。

衬底引发的损耗

硅衬底是半导体,根据掺杂浓度的不同可实现从 10kΩ ∙ cm(高阻硅)到0.001Ω ∙ cm的电阻率变化。片上螺旋电感与衬底间存在电容耦合和磁场耦合两方面。电容耦合使得总能量转变为一部分电能,使得品质因素下降。时变的磁场耦合会在衬底感应出涡流,产生欧姆损耗,从而进一步降低品质因数。通过合理的版图设计和工艺优化,可以有效的减轻电容耦合和磁场耦合,从而提高电感的品质因素。

电感优化实例

在充分理解电感的损耗机理前提下,我们可借助版图设计减小寄生,损耗等效应,从而提高电感的品质因素。如下介绍了分别从衬底损耗、导体损耗两方面的设计思路。

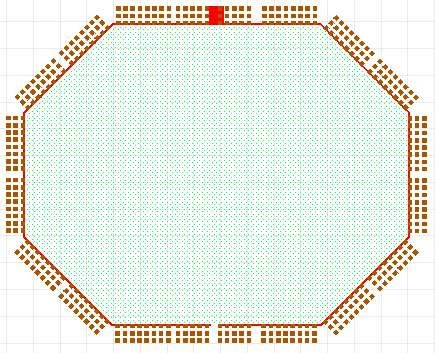

1.电源屏蔽设计

实现方式:在电感线圈外一定距离处,利用环状结构将电感与外围结构隔离开来,通常有多层金属的组成。此设计通过改善电磁兼容问题,来提高电感的性能。

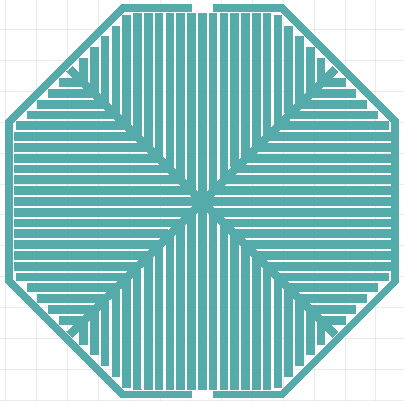

2.增加Sheilding设计

实现方式:在电感线圈正下方铺设金属,将电感与衬底有效的隔离开来。不同的Sheilding形状对隔离会有不同的效果,需要结合仿真结果和应用场景来具体分析。

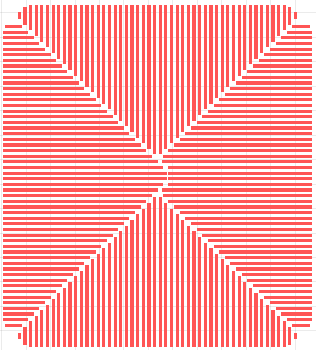

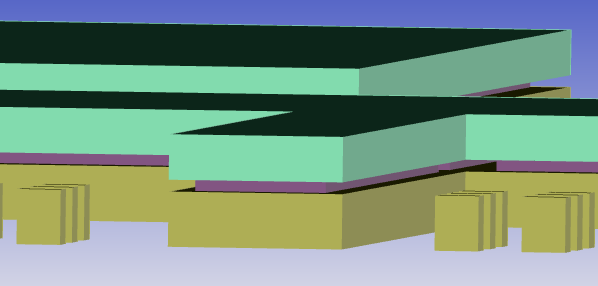

3.叠层电感设计

实现方式:螺旋电感的主线圈有三层形状一致的导体(两层金属,一层过孔)堆叠在一起。一般适合在有多个厚金属的工艺中。此方法通过增加电感线圈的厚度,来减小电感的欧姆损耗,更适合低频电感的优化设计。

总结

本文介绍了片上电感感值L,品质因素Q值的定义,并将品质因素作为电感优化设计的的目标;接着从金属损耗,衬底损耗两方面阐述了电感的损耗机理;最后围绕如何减小寄生和损耗这个核心问题,提出了一些电感优化设计的方法。