基于硬件仿真加速器的PCIe接口验证方法探究和实现

作者:郝强,工程师,上海高性能集成电路设计中心。

研究方向:集成电路系统级设计与验证

摘要:PCIe接口是处理器芯片上使用非常广泛的一种高速接口。通过PCIe接口,处理器可以与多种高速外部设备进行连接,完成不同场景的应用。因此,在处理器的RTL级设计开发阶段,对PCIe接口设计的验证显得尤为重要,需要通过不同的验证平台保证PCIe接口设计的功能正确性和性能稳定性。本文对基于Cadence 硬件仿真加速器创建处理器设计的PCIE接口验证平台的方法进行探究,同时结合实际项目完成该方法的实施,并完成该种验证解决方案的总结。

关键词:硬件仿真加速器 PCIe 验证方法

0.引言

随着处理器设计技术的不断发展,处理器的功能和性能得到极大的丰富和提升。其中,处理器总线技术的发展起着重大的推动作用。PCIe总线作为处理器系统总线的延伸,使得处理器可以与外部高速设备相连,能够完成多种应用功能扩展。因此,PCIe总线接口成为现代处理器设计中最为常用的外设接口之一。然而,PCIe总线协议相较于一般慢速的总线协议更为复杂,这就给PCIe接口设计的正确性带了挑战。为此,一般会寻求多种验证方法和手段来力求全面地保证PCIe接口设计的正确性。综合验证平台的高效性和验证场景的多样性考虑,采用基于Cadence硬件仿真加速器平台的PCIe接口的验证方法突出了开发周期短、运行速度快以及调试手段多的优势,日益成为PCIe接口设计验证最为重要的验证方法之一。本文描述了基于Cadence硬件仿真加速器对某款处理器芯片的PCIe接口设计进行验证的实现方法和验证环境的创建流程,用以满足该设计的验证需求。

1.待测设计简介

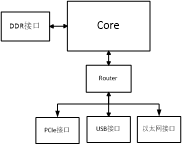

本待测设计是一款处理器芯片,集成多种I/O接口,其中PCIe接口符合PCIe 3.0链路标准,支持x4、x8和x16灵活配置,该设计接口配置为RC(Root Complex)工作模式。其结构如图1.1。该待测设计的核心通过路由部件与PCIe接口部件相连,可以实现DMA请求和MSI等中断请求。

图1.1

2.传统的验证方法

为保证处理器设计正确性,传统的验证方法包括软件模拟验证(Simulation)和FPGA原型验证(FPGA Protyping)。

软件模拟验证方法,是通过构建软件仿真验证环境,使用软件模拟器Simulator(例如NC-sim)加载RTL级设计和TestBench,并进行编译和施加测试用例来完成功能模拟。对于集成了PCIe接口的设计,还需要使用相应的VIP(Verification IP)作为EP(End Point Device),来模拟实现DMA访问和中断请求等验证。如图1.2所示。由于这些验证行为都是运行在软件层面,方便波形数据收集和查错,但是,一旦待测设计规模较大,尤其是处理器这种大规模复杂设计,整个验证环境的运行速度下降明显,施加一个测试激励往往需要几个小时甚至数十个小时,运行的时间开销是难以忍受的。

FPGA原型验证方法,是通过将RTL级设计使用FPGA资源实现,构建FPGA原型验证平台,进行实物验证。这种验证方法,运行速度快是其最大的优势,其运行频率最高能达到几十兆赫兹,比较适合进行连接真实设备对外设接口进行压力和稳定性验证。但是,FPGA原型验证平台开发和调试周期较长,往往只能在芯片开发的中后期才能投入使用。而且,根据FPGA实现的一些特殊性,一般需要对RTL设计进行适应性修改。另一个重点不足在于调试手段有限,设计运行过程中一旦出现问题难以快速定位。

因此,对于本文的待测设计的验证,尤其是PCIe接口验证不能只依赖于软件模拟验证和FPGA原型验证,还需要寻求其他更加有效、便于调试的验证方法。

3.基于硬件仿真加速器的验证方法

硬件仿真加速器验证技术,相对传统验证技术形成较晚,但随着各大EDA公司大力的投入研发和推广,已经成为一种成熟的验证技术,受到行业内的接受和认可,这其中,以Cadence公司的Palladium系列的硬件仿真加速器产品的表现最为突出。基于硬件仿真加速器的验证方法,相较于软件模拟验证,具有更快的验证速度和更真实的外设测试平台。而相较于FPGA原型验证,它具有更短的开发周期和更丰富的调试手段。因此,本文所提的待测设计在研发周期内,开发了多种基于硬件仿真加速器的验证平台,运用于系统软件调试、应用课题仿真和外设接口验证等。

本文将重点探究基于硬件仿真加速器验证平台在对PCIe接口设计进行验证中所采用的验证方法。

3.1 验证平台的整体结构

如前所述,PCIe接口属于高速总线接口,就PCIe3.0而言,可以支持2.5Gbps、5.0Gbps和8.0Gbps的传输速率,要直接在如此高的传输速率下进行仿真验证,对任何验证平台来说,都是一个不小的挑战。以Cadence公司Palladium Z1硬件仿真加速器为例,尽管其最高仿真运行频率可以达到4MHz,但仍然不能直接满足PCIe接口的标准要求。为此,Palladium平台提供了一套解决方案,通过使用SpeedBridge进行了快慢两端的速率适配。基于该解决方案,需要对处理器的PCIe接口部件进行修改。

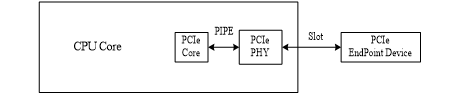

原始设计的PCIe接口应用场景如图3.1(a)所示,PCIe Core通过PIPE接口连接PCIe PHY,再通过其高速串行接口连接板级的PCIe插槽,最终与PCIe EP真实设备进行连接。

图3.1(a)原始的PCIe接口连接场景

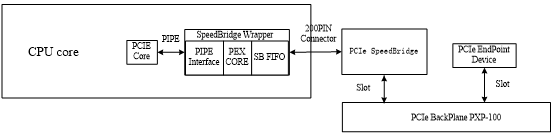

修改后的PCIe接口验证场景如图3.1(b)所示,由于PCIe PHY不可综合,不能直接在硬件仿真加速器上运行,因此,解决方案中提供了SpeedBridge Wrapper模块来进行替换,该Wrapper模块使用可综合代码实现,将其例化在处理器的PCIe接口设计中,其一端通过PIPE接口与设计进行连接,另一端输入输出端口映射到硬件仿真加速器的外部硬件接口引脚,再通过连接器电缆与PCIe SpeedBridge相连,PCIe SpeedBridge与PCIe EP设备安插到支持两个PCIe插槽的第三方底板上。这样就构建出了基于硬件仿真加速器的PCIe接口设计的验证平台。其中,带PCIe接口的处理器设计与SpeedBridge Wrapper运行在硬件仿真加速器上,以低速率通过PCIe SpeedBridge进行速率转换,实现了与外部高速率EP设备的通信。

图3.1(b)PCIe接口验证场景

在此解决方案中,运行在硬件仿真加速器上的PCIe接口设计可以与SpeedBridge Wrapper间使用2.5Gbps、5.0Gbps及8.0Gbps的传输速率进行仿真,因此,PCIe接口设计可以得到充分地验证。需要指出的是,PCIe SpeedBridge与外部PCIe EP设备只运行在2.5Gbps的速率,但这已经足够了。

3.2 验证环境内部实现

前面提到,运行在硬件仿真加速器上的PCIe接口设计,需要通过SpeedBridge Wrapper作为中间模块,与外部SpeedBridge进行连接,本节内容将进一步探究其实现方法。

PCIe接口设计与PCIe SpeedBridge Wrapper在本待测设计中都是使用Verilog编写,只需要按照模块间的一般连接方式实现即可。需要注意的是,这两者的连接,应该直接通过PIPE接口直连。

SpeedBridge Wrapper与硬件仿真加速器的外部硬件Pin脚是通过terminal映射方式,这就需要先将Wrapper的输入输出端口连接到验证环境顶层。通常的做法是,将Wrapper的端口引脚类似待测设计的子模块一样,自下向上一层一层地传递后,连接到最外层,作为验证环境顶层的输入输出。然而,这种做法比较繁琐,需要大量修改待测设计各个关联层次的端口数量,而且,也会在一定程度上增加了待测设计代码的后期修改维护的工作量。因此,硬件仿真加速器提供了另一种实现方式,即在预编译之前,通过globalNet命令将需要引出的内部信号声明为global net,这样就可以在环境顶层直接使用,省去了模块间的穿透,这大大减少了代码修改的工作量,这是比较推荐的做法。

定义了globalNet之后,就可以通过cableConnection指定硬件仿真加速器与外部Target系统的连接接口类型,即与外部PCIe SpeedBridge连接的硬件接口类型,在Palladium Z1硬件仿真加速器上,需要使用TPOD接口。

选择硬件接口之后,就需要对terminal进行物理关系映射,同时,设置合适的时序约束。

图3.2-1 SpeedBridge Wrapper端口物理映射流程

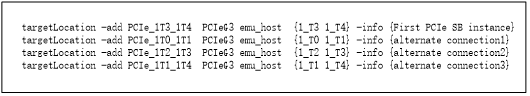

在targetLocation配置时,除了首选的TPOD资源配置之外,可以额外配置几组以备选,便于在运行阶段,按照可用资源进行灵活选择,避免了再次分配资源进行重复编译。

图3.2-2 target配置多选示例

在完成了PCIe SpeedBridge相关的硬件接口配置之后,就可以进行硬件仿真加速器验证环境的编译和后续运行了。需要注意的是,编译和运行的模式需要设置为In-Circuit Emulation即ICE模式。

实际上,Cadence已提供了较多基于SpeedBridge使用示例流程,诸如PCIe、Ethernet、USB等等,用户可以比较轻松地按照示例进行验证平台的创建,并且可以快速地投入相关验证工作。

3.3 验证调试方法

PCIe设计接口的验证需要面向多种应用场景,这也就为查错和调试带来难题。基于硬件仿真加速器的验证平台,在为用户提供较高的工作频率下,也为用户开发多种调试手段成为可能。

在该待测设计中,主要经历了三种调试阶段。

(1)基于操作系统内核和用户测试程序信息的粗粒度调试阶段

正是由于硬件仿真加速器的运行速度快的优势,使得在处理器设计开发初期,就可以运行操作系统和用户测试程序。这样,通过操作系统内核信息和用户测试程序调试信息就可以判断出错位置,为后续调试指明方向。这个阶段可称之为粗粒度的调试阶段。

(2)基于SDL动态监测的中粒度调试阶段

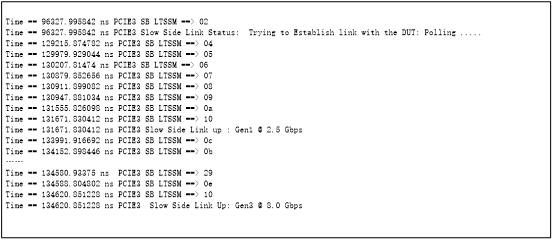

SDL(全称为State Description Language),是Palladium硬件仿真加速器所支持的调试脚本语言,它可以调用相关命令控制硬件仿真加速器的运行和交互,比如,暂停待测设计的运行、设置触发条件、捕获波形、以及显示内部设计信号值等等。通过SDL实现的Monitor,可以实时监测PCIe设计接口重要的内部状态和事务数据报文,便于进一步问题定位。但受硬件资源限制,监测的信号量还是有限,因此,这个阶段称之为中粒度的调试阶段。

图3.3-1 SDL Monitor状态监测示例

(3)基于波形分析的细粒度调试阶段

通过前两个粗粒度、中粒度的调试阶段,问题已经能够锁定一个出错区间了。此时,可以在硬件仿真加速器验证环境下设置触发条件,捕获波形,来精准分析出错现场。支持全波形记录,使得硬件仿真加速器在调试方法上能与软件模拟验证相媲美,方便用户细粒度的分析调试。

4.总结

通过使用基于Cadence硬件仿真加速器进行PCIe接口验证的解决方案,大大提升了本文中待测设计的PCIe接口验证效率。不管是相比软件模拟验证的运行加速,还是相比FPGA原型验证的易于开发调试等,都突出了自身显著优势。当然,本文中对基于硬件仿真加速器的PCIe接口验证方法的探究还比较粗浅,需要在后续项目中,进一步深挖和改进,以待能全部发挥Cadence硬件仿真加速器的优秀性能。

5.参考文献

[1]王奇.PCI Express体系结构导读.北京:机械工业出版社,2010.3.

[2] Cadence.vxeUserGuide.pdf.

[3] Cadence.vxecmdref.pdf.

[4] Cadence.PCIExpress3 0_SpeedBridge_User_Guide_1.5.pdf.

[5] Cadence.sdl_training.pdf.